Features added around 400ZR aims to bring order to 400ZR+

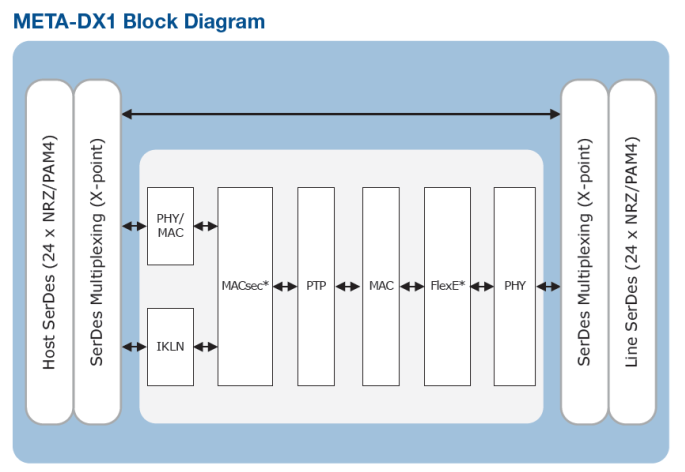

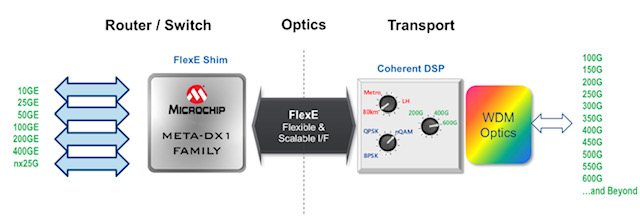

The OIF has started a project to combine Flexible Ethernet (FlexE) technology with the 400ZR coherent interface standard.

400ZR is designed to transmit a 400 Gigabit Ethernet (GbE) signal over at least 80km using coherent optical transmission.

Adding FlexE technology will enable 4x100GbE signals to also be transmitted.

Separately, the OIF has started a project to create a 96 gigabaud (GBd) coherent driver modulator specification. Such a symbol rate enables 800 gigabits of data to be sent using a single carrier.

400ZR and 400ZR+

The 400ZR was developed to create an interoperable, low-cost 400-gigabit coherent interface.

The 400ZR specification leaves open the type of optical module to be used but the industry is adopting such pluggable form factors as the QSFP-DD and OSFP.

Karl Gass

“Pushed by our network operator members, the goal of 400ZR was that this would be a cost-driven project,” says Karl Gass, OIF physical and link layer working group, vice-chair optical. “It would have a specific function and everything would be optimised for that function.”

But those companies developing coherent digital signal processors (DSPs) say the 400ZR market alone will be insufficient to recoup their development costs. These players want to develop enhanced designs that extend the optical performance and the overall market, a module design category known as 400ZR+.

Optical performance can be enhanced in several ways for the 400ZR+. One way is to improve the performance of the forward error correction at the receiver to enhance the optical gain, even if by fractions of a decibel.

Another is to adopt several modulation schemes whereas the 400ZR uses 16-ary quadrature amplitude modulation (16QAM). The ability to send lower data rates than 400 gigabits will also enhance the transmission distances beyond ZR’s 80km.

“The problem with 400ZR+ is that, unless you are coordinating with the other DSP vendors, you are not going to get interoperability,” says Gass.

The OIF did not take responsibility for coordinating 400ZR+ and, in retrospect, that was a lost opportunity, he says.

Combining FlexE with the 400ZR design is the OIF’s attempt to ‘reign in’ some of that ZR+ functionality.

“We’ve got a couple of things behind the scenes where we are saying: this is not ZR but in implementing ZR+, there are opportunities for interoperability,” says Gass.

The OIF is all for differentiation in the marketplace, stresses Gass, “but for 400ZR+, we left the opportunity for differentiation to be too big.”

>

“The problem with 400ZR+ is that, unless you are coordinating with the other DSP vendors, you are not going to get interoperability”

Flexible Ethernet

Adding FlexE will enable 4x100 Gigabit Ethernet (GbE) signals to be transmitted over a 400-gigabit wavelength, whereas 400ZR transmits a 400GbE signal only.

The OIF-defined FlexE has several attributes: it enables the bonding of Ethernet channels, allows sub-links where data can be sent over lower speed links and supports non-standard Ethernet client rates.

The OIF wants the industry to get on the 400ZR bus

For the latest OIF project, FlexE will be used to bond the 100GbE channels. And four channel of 100GbE will not necessarily be the sole additional implementation.

“That will be one of the things covered but I don’t want to say that it will be the only thing covered,” says Gass. “But 4x100GbE is the specific example used for the project start.”

The FlexE can be added on the board alongside a 400ZR module or it can be added within the module, in which case it becomes a 400ZR+.

“If we get multiple people to sign up to that, it benefits the market by showing additional points of interoperability,” he says. But the issue is that there will be no guarantee that FlexE will be embraced in every 400ZR+ module.

The project’s outcome will be published by the OIF as a white paper.

Coherent driver modulator

The second OIF project started will specify a new generation of coherent driver modulator supporting a symbol rate of 96GBd.

The project follows the OIF’s Implementation Agreement published in late 2018 that specifies a 64GBd coherent driver modulator, work that began in October 2016.

Developing an Implementation Agreement ensures that there is a common standard for companies developing the higher baud rate coherent driver modulator.

“This project is different to some of our other coherent work where we are more focussed on size; this one is focussed on performance,” says Gass.

The OIF does not specify the modulator type used for the design and the assumption is that lithium niobate, indium-phosphide and silicon photonics technologies will all be used to implement the design. But each technology will need to meet the final specifications agreed upon.

“I don’t want to make it [the driver modulator project] sound easy but it is going to be the same people that worked two years ago on the RF bandwidth issues for the 64 gigabaud version,” says Gass.

Timescales

The higher baud rate coherent driver modulation Implementation Agreement is expected to be completed in 18 months.

The FlexE-400ZR white paper will be completed sooner as this is more pressing. “There are several implementations that are already in silicon,” says Gass.

The first 400ZR coherent pluggable modules are expected in the first half of 2020.

ECI Telecom details its cell-site gateway for 5G

ECI Telecom has unveiled its cell-site router for 5G that also supports existing 3G and 4G wireless standards.

Jimmy Mizrahi

“You need to support the existing one or two generations of cellular networks,” says Jimmy Mizrahi, ECI’s executive vice president and head of global portfolio.

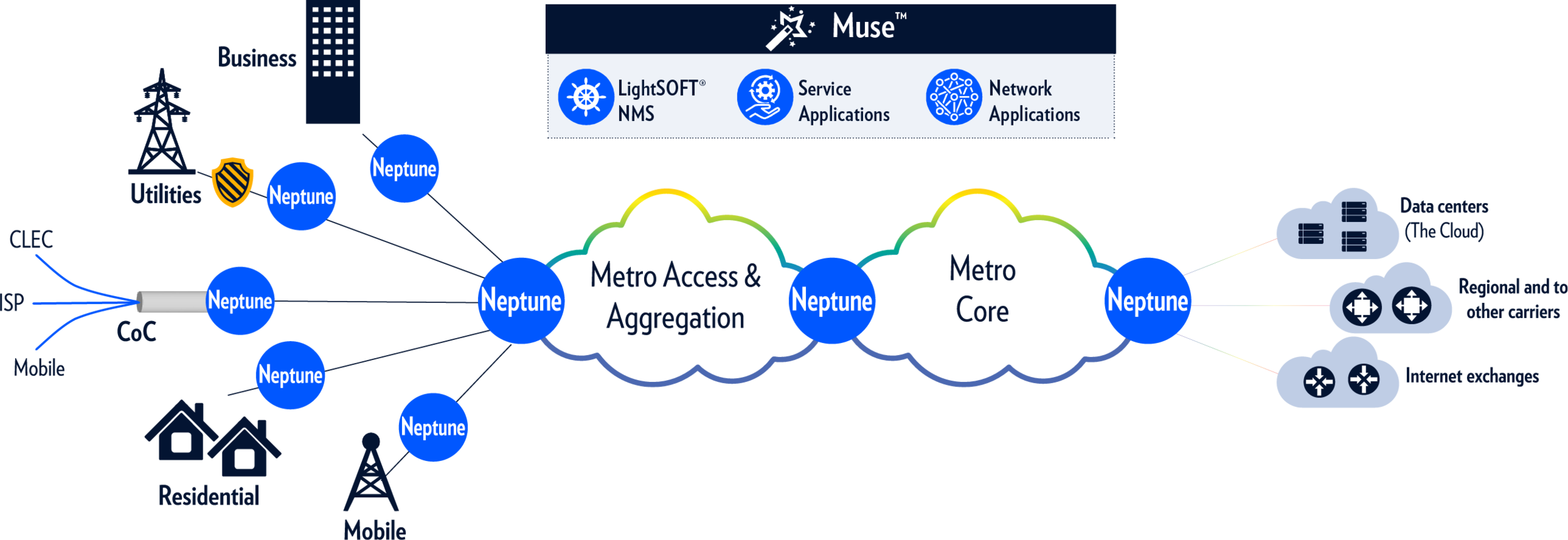

The platform, the NPT 1022 cell-site router, is the first of several platforms that ECI will launch for 5G as it upgrades and expands its Neptune product line.

“The 1022 is part of a new line of products covering all layers of the network, starting at the cell site and going to aggregation and the metro core,” says Ezra Yehezkel, product line manager, packet transport solutions at ECI.

The Neptune portfolio will include a high-capacity packet-processing platform that can scale to 16 terabits.

Mobile backhaul player

ECI has been addressing the mobile backhaul market since the advent of GSM.

“We are now deploying 4G around the world, while in India we are one of the biggest vendors, if not the leading one, in mobile backhaul,” says Mizrahi.

ECI’s Indian operator customers include Bharti Airtel, Vodafone India and Idea Cellular; the latter two now Vodafone Idea after a merger.

The systems vendor started developing its 5G portfolio two years ago and is now engaged with more than 20 communications service providers around the world. “Some of them are the largest in the market,” says Mizrahi.

He segments the 5G market operator opportunity into three. The first category is the early adopters that have started or are planning to deploy 5G. “We have a proof-of-concept [deployment] with one of the largest service providers in the world and in the next few months they will start to deploy 5G,” says Mizrahi.

The second category is those operators that are issuing tenders for 4G but want to be ready for 5G, says Mizrahi: “They don’t want to continue investing in their existing networks knowing that in the next several years they will have to invest in 5G.”

The final class is the late-adopters; operators that are waiting to see how 5G develops.

Source: ECI Telecom

NPT 1022

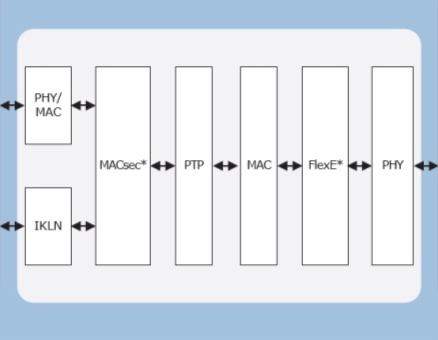

The NPT 1022 is deployed at a cell site and is designed to operate in harsh environments. The platform is one-rack-unit (1RU) high and uses Broadcom’s Qumran-UX Ethernet switch chip for an overall switching capacity of 64 gigabits.

“Our target with this platform is to do the optimisation when you need 10-gigabit uplinks; for 100 gigabits we have other platforms,” says Yehezkel.

Ezra Yehezkel

The 1022 platform supports the stringent timing requirements needed for 5G, known as Class C and Class D synchronisation that have a timing accuracy of +/-10ns and +/-5ns, respectively.

Another key 5G feature is network slicing; the mechanism whereby the 5G network can be segmented to meet varied, and sometimes conflicting, service requirements.

Network slicing is used in other ways too. It can enable two operators to pool their investments to roll out a 5G network yet run the infrastructure as two networks.

Network slicing will also allow an operator to run several generations of wireless on their network, adds Mizrahi.

There are two aspects to networking slicing: hard slicing that dedicates network resources to specific services, and soft slicing that prioritises and optimises the use of shared resources.

“Hard slicing requires changes in the a platform’s backplane; you have to map specific lines in the backplane to support hard slicing,” says Mizrahi. It means supports the OIF’s Flexible Ethernet standard; that and hard slicing being part of the ITU-T’s Metro Transport Networks (ITU-T G.mtn) specification.

Soft slicing is described by Mizrahi as an enhancement to existing virtual private networking (VPN) technology.

ECI points out that hard slicing is not a feature needed for the 1022 given it resides near the network edge but it is a feature that will be included in the new cages that will make up its 5G portfolio.

“We can do soft slicing with the option of hard slicing,” says Mizrahi.

>

“To my knowledge, no white box currently has the performance and functionality provided by the 1022”

White Boxes

Two white-box designs for cell-site gateways already exist, one as part of the Open Compute Project - the AS7316-26XB that is backed by AT&T - and the Odyssey Disaggregated Cell Site Gateway (Odyssey-DCSG) developed under the auspices of the Telecom Infra Project (TIP).

“The reason we decided not to use a white box is that we wanted to optimise the configuration to what we believe customers need,” says Mizrahi.

Cell-site gateway platforms will be deployed in the hundreds and thousands of units by an operator, making them highly cost-sensitive. As a result, no one box will fit all the configurations while meeting the operators' target price.

“The question here is also not just about price but also functionality,” says Mizrahi. “To my knowledge, no white box currently has the performance and functionality provided by the 1022.”

Availability

The 1022 is already shipping and is deployed in one network carrying live traffic. ECI expects the platform to be generally available in the coming month.

“As soon as the software will be generally available we will start deployment in multiple networks around the world,” says Mizrahi.

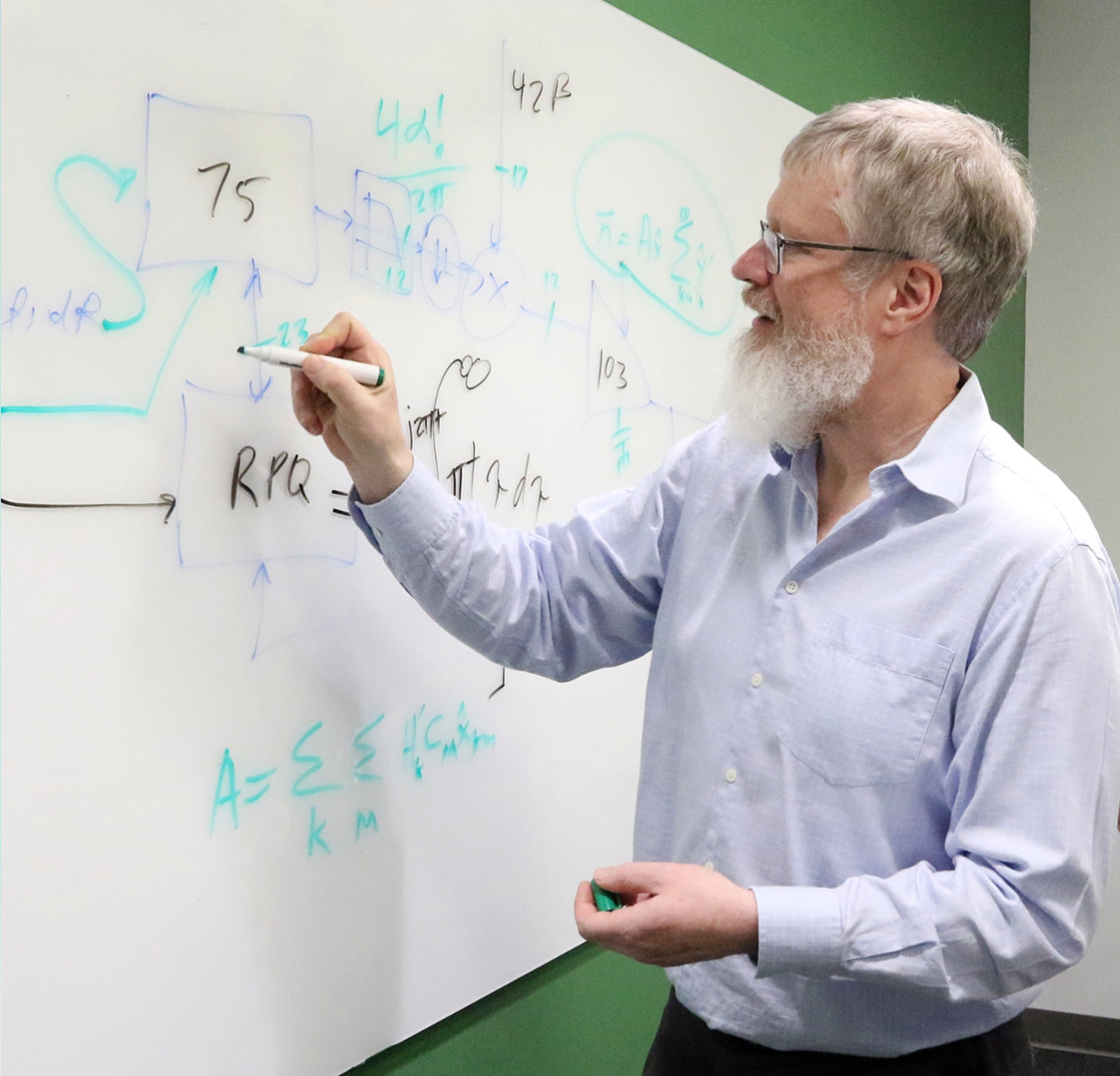

Infinera prepares for first ICE6 coherent DSP samples

Infinera has taped out its 7nm CMOS FlexCoherent 6 digital signal processor (DSP) and expects samples of the coherent chip in the next fortnight.

Rob Shore

“We are ready to start fabricating prototype modules,” says Robert Shore, senior vice president of marketing at Infinera (pictured).R

The DSP, along with Infinera’s photonic integrated circuit (PIC) that was demonstrated at the OFC show held in March, will be integrated into a module that supports two wavelengths, each capable of supporting up to 800 gigabits of data.

The company expects to have a prototype of the 1.6-terabit Infinite Coherent Engine 6 (ICE6) module by year-end, while the first ICE6-based products are scheduled for the second half of 2020.

Core, edge and cognitive networking

Infinera outlined its networking vision earlier this year after the acquisition and incorporation of Coriant.

Dubbed Infinite Network, the vision covers the core and network edge as well as cognitive networking whereby the network makes intelligent decisions and adapts using status data collected from the network (see diagram).

Source: Infinera

For the core, the focus remains to advance the capacity and reach of optical transmissions. “There is no question that long-haul and subsea networks need this kind of functionality,” says Shore.

The latest coherent systems coming to market have much greater flexibility and programmability. “There are a lot more knobs to play with,” says Shore.

The changeable parameters include symbol rate, modulation scheme as well as probabilistic constellation shaping that is used to fine-tune the data rate to better exploit the capacity available on a given route.

At the network edge, the adoption of cloud technologies is causing change. Such cloud deployments not only include distributed data centres in the metro but also multi-access edge computing located in building basements and at cell towers.

Such deployments mean applications will become more distributed leading to massively dynamic traffic patterns, says Shore. In turn, the traditional networking model whereby thousands of endpoints are aggregated in the metro network before being passed onto the core will no longer hold.

“There is a need to classify that traffic close to the edge, handle the traffic on a flow-by-flow basis, and connect the end-user to the application without backhauling it,” says Shore.

Classifying traffic implies IP and that is an area Infinera is addressing with its disaggregated router strategy. But there is also a coherent opportunity here: the growth in edge-network traffic is outpacing the ability of direct-detect optics. “This increases the opportunity for edge-optimised coherent-based solutions,” says Shore.

ICE6

Infinera has enhanced its PIC and coherent DSP technology for its ICE6 coherent module.

The current ICE4 uses two PICs: one for the transmitter and one for the receiver. The PICs support up to 1.2 terabits, six channels each capable of transmitting up to 200-gigabit signals using 16-ary quadrature amplitude modulation (16-QAM). The ICE6 uses one PIC that supports two optical channels for a total capacity of 1.6 terabits.

Meanwhile, the FlexCoherent 6 implements coherent toolkit features such as sub-carriers, soft-decision forward-error correction (SD-FEC), and probabilistic constellation shaping.

Earlier this year, Infinera outlined two planned module options, one addressing the core, the ICE6c, and a second for the edge, dubbed the ICE6e.

The ICE6e was also a two-channel module but tailored for the metro, with lower optical performance and lower power consumption. However, the merit of such a metro module has become unclear in the era of the 400ZR interface, says Shore.

Infinera continues to monitor the 400ZR pluggable module opportunity but admits it has less significance for the company. “The 400ZR is really for short distance, point-to-point links,” he says.

The 400ZR+ that extends 400-gigabit coherent performance to metro distances has still to be specified. Like the ZR, it will be implemented using a pluggable module such as the QSFP-DD or the OSFP. However, while the 400ZR+ is not a direct competitor to the envisaged ICE6e, it would overlap.

For now, the ICE6e has been demoted with Infinera focusing on the flagship ICE6 module for the core while investigating other coherent options for the metro.

Infinera has already mentioned a pluggable module design which would take a 400-gigabit input and convert it to lower streams, for example, operating at 100 gigabits or 25 gigabits, and implemented using a ‘virtualised laser’.

Unlike the 400ZR which supports a 400-gigabit link only, such a design suits metro-access, taking multiple streams from the access network.

“This is a different approach to metro-optimised optics and might be an alternative to ZR, ZR+ as well as something like the ICE6e,” says Shore. For now, the company is not ready to add further detail.

Coherent toolkit

One key feature of the latest FlexCoherent 6 DSP is its support for Nyquist sub-carriers.

Infinera first announced its adoption of sub-carriers in 2016. Here, multiple Nyquist sub-carriers are spread across a channel instead of modulating the data onto a single carrier.

The benefit is that high data rates are possible while the baud rate used for each individual sub-channel is much lower, and a lower baud rate is more tolerant to non-linear channel impairments during optical transmission.

Sub-carriers improve spectral efficiency as the channels have sharper edges that enable tighter packing.

The ICE4 DSP was Infinera’s first design to use sub-carriers, adopting four or six per channel, for example. The FlexCoherent 6 is more sophisticated using eight sub-channels, each independently controlled and operating at 11 gigabaud (GBd) for an overall baud rate of 88GBd.

Source: Infinera

Source: Infinera

“We apply probabilistic constellation shaping to each sub-carrier,” says Shore. “This enables dynamic bandwidth allocation where we can increase or decrease the amount of bandwidth on each sub-carrier.”

This allows more data to be sent on the inner sub-carriers and less data on the two outer sub-carrier signals that are typically harder to recover.

Shore says that the sweet spot for sub-carriers is 8-11GBd and that the number of sub-carriers used can be changed to remain within the sweet-spot region (see diagram above). Infinera says the overall aggregate baud rate can go up to 94GBd.

Another feature of the DSP is its use of SD-FEC gain sharing. By sharing the FEC codes, processing resources can be shifted to one of the two optical channels that needs it the most. The result is that some of the strength of the stronger signal can be traded to bolster the weaker one, extending its reach or potentially allowing a higher modulation scheme to be used.

Infinera also uses a single oscillator for both of the module’s optical channels. This avoids having to use extra channel spacing to cater to the independent laser drift when two oscillators are used, one for each laser. Using a single oscillator thus benefits spectral efficiency.

Infinera expects to announce more details related to its metro plans at the upcoming ECOC show in Dublin in September.

“It [the announcement] will play very nicely with metro-style white-box routers,” says Shore.

ADVA runs the rule over its TeraFlex platform

Gazettabyte talks to Jörg-Peter Elbers about the recent trial of ADVA’s FSP 3000 TeraFlex platform in Tele2’s network and gets his views on industry trends.

It is early morning and the air is cool. I'm seated outside at a coffee bar in Herzliya’s marina awaiting Jörg-Peter Elbers, senior vice president, advanced technology, who is in Israel visiting local ADVA staff.

He arrives as the bar opens and we are the only customers.

Just as we are about to start, the waitress informs us that the barista has yet to arrived. Breakfast can be ordered but we must wait for coffee.

Flexing the TeraFlex

ADVA trialled its TeraFlex platform on a Tele2 route between Tallinn and Frankfurt.

First detailed in 2017, the TeraFlex is a one-rack-unit (1RU) stackable chassis that supports three hot-pluggable 1.2-terabit modules or ‘sleds’. Each sled uses an Acacia AC1200 coherent module that supports two line-side wavelengths, each capable of coherent transmission at up to 600 gigabits-per-second (Gbps).

The TeraFlex was designed to address the needs of large-scale data centre operators that want power-efficient, high-capacity and compact platforms. But interest in the platform has broadened to include telcos and research and educational network operators.

For the trial, the transmission distance was increased by using loopbacks at the route’s locations. From an operational perspective, it means equipment is needed at one site only. The network also features reconfigurable optical add-drop multiplexers (ROADMs) at all the intermediate sites.

Data was sent in 100-gigabit increments over a spectral slice. A spectral slice is a relatively new concept whereby an operator leases a portion of the unused spectrum on a fibre to interested third parties.

The optical performance achieved includes sending a 500-gigabit optical signal over 1,016km and a 200-gigabit signal over 5,738km.

The TeraFlex has also been trialled by Telecom Italia in its backbone network. A 600Gbps wavelength was sent over a distance of 100km on an optical route designed for 10Gbps while a 300Gbps signal was sent over a distance of 2,500km.

ADVA used network telemetry data gathered by the TeraFlex to boost overall optical performance. “That was also an intention of the trial: how hard can we drive the system and what is the top-line performance we can get,” says Elbers.

The TeraFlex has also been trialled by Telecom Italia in its backbone network. A 600Gbps wavelength was sent over a distance of 100km on an optical route designed for 10Gbps while a 300Gbps signal was sent over a distance of 2,500km.

Differentiation

ADVA dismisses the notion that TeraFlex’s optical performance is dictated solely by Acacia’s AC1200 module such that the scope for platform differentiation is limited when compared with competitors’ designs that also use the Acacia module.

“The TeraFlex does use certain hardware but there is a tremendous amount of configuration flexibility, literally thousands of configurations you can use,” says Elbers.

These include different modulation formats and whether fractional quadrature amplitude modulation (QAM) is used. Fractional QAM is a feature of Acacia’s coherent module whereby two adjacent modulation formats, for example, 8-QAM and 16-QAM, are each used for a percentage of the transmission time to fine-tune the data rate. The baud rate for a given data rate can also be altered to adapt the spectrum used for the transmission.

For the trial, a QPSK reference signal was first sent, a signal that will go the furthest. Based on the performance achieved, a decision is made as to whether the data rate transmission performance can be bumped up, says Elbers.

Networks are run conservatively, he says. At the start of a link’s life, the large safety margin built-in can be exploited to cram more data across a link.

“I might run into issues at the end of the life of the system but I can drive the system harder at the beginning,” says Elbers. “The result is more capacity from the start and better economics.”

Elbers says that optimising the network, even at its end-of-life stage, by exploiting the capacity available in each slot and optimising the spacing and data rate, a 30 percent capacity improvement can be achieved compared to a non-optimised network.

But the bigger potential is if the operator is willing to operate the line system using lower margins, adjusting as required over its operational life, whereby a doubling of capacity is possible.

Jörg-Peter Elbers

600G versus 800G

Elbers says that there is a market perception of a 600 gigabit-class of coherent performance and an 800 gigabit-class. Systems vendors Ciena and Infinera have announced solutions that deliver 800 gigabits per wavelength.

But such solutions do not yet exist, he says, adding that operating at a lower symbol rate per wavelength results in a lower implementation penalty. “Components are imperfect compared to the theoretical performance and the closer you stay with the maturity curve of the technology, the lower the delta is,” says Elbers. “With 60 gigabaud [GBd] and QPSK modulation, you are very close – sub 1 decibel - from the theoretical performance; that is what we can get.”

ADVA also points out that a TeraFlex sled can deliver 1.2 terabits using two optical wavelengths and a single coherent DSP.

For the Tele2 trial, the TeraFlex also delivered 800 gigabits of data using a 125GHz-wide channel. “This was a superchannel configuration,” says Elbers.

The AC1200 can operate close to 70GBd while Infinera’s ICE6 will operate at 88GBd using sub-carriers while Ciena’s WaveLogic 5 can operate at up to 95GBd.

“There are certain technology evolution steps; 95GBd appears a half step,” he says. The industry has gone from thirty-something to sixty-something gigabaud and now the aim is to double it again. Elbers believes 120GBd and even 140GBd will be possible.

“It is not just the building blocks but integration which will form more and more a key part,” says Elbers. “Bringing everything as close together as possible.” This is needed to tackle the ever-increasing challenge of radio frequency (RF) design as the symbol rate continues to rise.

Acacia’s acquisition

When Cisco announced in July its intention to acquire Acacia, ADVA commented that such developments are to be expected as networks become more open and disaggregated.

ADVA also pointed out that Cisco intends to run Acacia as a component business unit and will continue to sell to all equipment makers while Ciena’s Optical Microsystems unit is making its WaveLogic coherent DSPs and module technologies available to the wider market. And with companies such as NEL and Inphi, merchant DSP experts will continue supplying the market.

While not going into detail, Elbers points out that it is common practice to have clauses in contracts that ensure continuity of supply under such circumstances. He also adds that designing in another coherent DSP into a platform such as the TeraFlex is “a big decision” but that the TeraFlex has been architected with such modularity in mind.

Vertical integration

ADVA has a team that addresses the company’s technology needs to help the company decide whether to make or buy. “What areas makes sense for us to do on our own and which areas does it make sense to just buy from a merchant vendor,” says Elbers.

The company has always designed its optical amplifier solutions and developed its MicroMux solution that allows low-rate client signal interfaces to interface efficiently to the high-capacity TeraFlex.

Only a few companies will continue to make their own coherent DSPs, he says, especially as next-generation designs move to the costly 5nm CMOS process.

Silicon photonics design expertise is another skill ADVA has. “Silicon photonics democratises component development and we have activities in that area involving coherent engines and optics and we see the potential there,” says Elbers.

Our interview ends and we make our way to a taxi rank beyond the marina so that Elbers can travel to Ra’anana where one of ADVA’s two local offices is located.

We find a driver before realising he is not first in the rank. The cab driver that is first in the rank strides towards us and a heated discussion between the drivers ensues. Agreement is reached and we move to the first cab but not before Elber’s new driver restarts the argument. Eventually, Elbers sets off for the rest of his day.

The morning air has heated up.

Cisco-Acacia blurs the optical ecosystem vendor divide

Cisco Systems’ acquisition of Acacia Communications would make it first to market with a 400ZR pluggable coherent interface. So claims Vladimir Kozlov, CEO of LightCounting Market Research.

“This is the main reason Cisco is doing the deal,” says Kozlov. “It is very important for Cisco to get its core routers with DWDM optics and push network evolution in this direction.”

Cisco is keen to grow its market share among service providers and lead in the development of software for automating telecom networks centred around routers, he says: “This will be the best way for Cisco to re-energise its optical transport business.”

Tom Williams, Acacia

“We are planning to sample [the 400ZR] before the deal closes,” says Tom Williams, vice president for marketing at Acacia. “Our plan is to be first to volume, that is the most important thing.”

The acquisition is expected to be completed in the second half of Cisco’s fiscal year, 2020 (February-July 2020).

Optical acquisition

Acacia is a merchant supplier of coherent digital signal processors (DSPs). The company also sells photonic integrated circuits (PICs) and coherent optical modules that address data centre interconnect, metro, regional, long-haul and subsea networks.

Its latest 1.2-terabit AC1200 - a two optical channel module, each wavelength capable of supporting up to 600 gigabits-per-second - addresses all these applications.

Acacia has enabled system vendors without coherent solutions - firms such as ADVA, Fujitsu and ZTE - to compete with the likes of Ciena, Huawei, Infinera and Nokia that own coherent technology. A successful acquisition will remove the industry’s leading independent supplier of coherent technology.

>

“We are planning to sample [the 400ZR] before the deal closes”

It is very important for Cisco to get its core routers with DWDM optics and push network evolution in this direction

Bill Gartner, senior vice president and general manager, optical systems and optics, Cisco, stressed during last week’s webcast announcing the deal that Cisco will remain committed to Acacia’s business including Acacia’s existing and new customers.

Cisco will pay $2.6 billion for Acacia. The fee is based on a valuation of $70 per Acacia share, a high purchase price.

“The $70 price is about 33x the 2020 earnings,” says James Kisner, a financial analyst and contributing consultant at LightCounting. “That’s pretty high for any communication equipment company.” But while the multiple may be high, Acacia is expected to grow earnings 27 percent in 2020. “So 33x isn’t crazy if you believe such expectations,” says Kisner.

The deal will also require the approval of the Chinese regulator given Acacia’s business with vendor ZTE and possibly FiberHome.

Strategic thinking

Cisco says that silicon, optics and software are foundational technologies that underpin its success in the marketplace. Buying Acacia with its silicon photonics and coherent expertise will further enhance its silicon and optics portfolios, it says.

>

“It is very important for Cisco to get its core routers with DWDM optics and push network evolution in this direction ”

The company also points to exponential growth in traffic that is fuelling demand for high-speed network infrastructure. “We believe these dynamics are creating an environment where our customers are needing to increasingly adopt faster speed networking technology - 100-gigabit, 400-gigabit and higher - to support higher bandwidth demands,” says Cisco’s Gartner.

Cisco sees Acacia as a key asset to be able to address the transition of coherent optics from optical chassis-based systems to pluggable technology.

Even with all three [LightWire, Luxtera and Acacia], we still don’t have the critical mass to go after all of the different silicon photonics opportunities

The move is motivated by data centre players and now service providers wanting to remove the media-converter function such as a transponder or a muxponder. “These have trended in the last few years from line cards that get used by a lot of service providers to pizza boxes that get consumed in data centre content providers,” says Ron Johnson, senior director, optical systems, Cisco. “And now we are seeing service providers starting to use these pizza boxes as well.”

Typically a core router using 100-gigabit grey optics interfaces to a transport box that multiplexes such streams for DWDM transmission. Placing the DWDM optics in a pluggable directly on a router or switch simplifies the task to then aggregating the optical signals for transmission.

Sterling Perrin also highlights the opportunity for pluggable optics, specifically at 400 gigabits.

“This is where the client-side and line-side optics will become the same size, eliminating the faceplate tradeoff problem that dogged IP-over-DWDM for decades,” says Perrin, principal analyst optical networking & transport at Heavy Reading. “We know the cloud/ webscale market will go for integrated pluggables on routers. What’s not known is when and how much this will appeal to traditional telecom operators.”

Johnson admits that he struggles to predict how quickly pluggables will cannibalise the non-pluggable market because there are complications. One issue is the organisational boundaries within service providers between their packet and transport systems teams.

One system vendor told Gazettabyte that while pluggables will become an increasingly significant part of the coherent market, it will only account for a third of the total market by 2024, with transport platforms accounting for the rest.

Industry change

The Cisco-Acacia deal highlights the ongoing consolidation taking place in the optical industry.

Sterling Perrin, Heavy Reading

The announced deal follows Lumentum’s acquisition of Oclaro, Infinera’s acquisition of Coriant, II-VI’s acquisition of optical component leader Finisar, and Cisco’s acquisition of Luxtera.

At the OFC show in March, Paul Brooks, director of strategy for lab and production at Viavi Solutions, highlighted the change sweeping the industry. He pinpointed three drivers, all beginning with the letter ‘C’: consolidation, commoditisation, and China.

George Notter, an equity analyst at Jefferies, points out in a research note that the purchase highlights two ongoing trends in the optical industry: how the pace of innovation in the optical industry is accelerating, and how bigger and bigger R&D budgets are needed to keep up.

Smaller optical suppliers will struggle to keep up with vendors such as Ciena and Nokia which have sizable R&D budgets, he says.

Vertical integration

The Acacia deal also highlights the trend of how systems vendors are becoming more vertically integrated.

Ciena stressed its greater vertical integration at the recent launch of its WaveLogic 5 coherent DSP family. Huawei is doing the same, in part to strengthen its technological independence. Infinera has its longstanding indium phosphide PIC technology as well as its in-house coherent DSP that it is using for its latest coherent engine design, the ICE6. The ICE6 will support 800-gigabit wavelengths as will Ciena’s WaveLogic 5.

Ron Johnson, Cisco

For Cisco, being more vertical integrated is important. “There is a pretty significant use of Acacia’s technology in the optical platforms and that has grown over time,” says Johnson. “With the acquisition, we eliminate the margin stack in these situations.”

In turn, the latest coherent DSPs are implemented in state-of-the-art 7nm CMOS which is costly, as is the development of the algorithmic techniques they implement. And the chip development costs will only rise. Cisco’s deep pockets will help Acacia’s development work in this respect.

Opportune exit

LightCounting takes another angle on the deal, explaining how Acacia has chosen an opportune moment for exiting.

Acacia’s growth was hampered by the trade war between the US and China in 2017-2018. The ZTE ban in April 2018 and Huawei ban in May 2019 has impacted the company’s valuation, given that ZTE remains Acacia’a largest customer and that FiberHome may also be using Acacia’s products. “The long term risk associated with doing business in China is a significant problem for the company,” says LightCounting.

In turn, Chinese equipment vendors ZTE and FiberHome are following the example of Huawei in developing semiconductor ICs, optical components and modules to ensure their supply. The Chinese government is also prioritising domestic manufacturing of IC and optical chips, including coherent DSPs, and is investing heavily in start-ups such as Wingcomm.

The merchant market is also limited for Acacia given the dominance of the large optical transport equipment vendors that own coherent technology.

And longer-term, opportunities such as 400ZR and even 10km-reach 800-gigabit optics also have risk factors in terms of their timing, given the slower-than-expected demand for high-speed optics from the cloud companies in late 2018 and early 2019.

All these issues suggest Acacia is prudent to join forces with Cisco, says LightCounting.

More consolidation?

The deal also raises questions as to the strategy of those system vendors that use third-party coherent DSP technology and even their fate.

Michael Genovese, managing director of financial analyst firm, MKM Partners, says Cisco's purchase of Acacia has major industry implications, including the potential end of the merchant DSP market.

The formerly clean delineation between component houses and system vendors has started to blur

“Merchant DSP has allowed Tier 2 and Tier 3 optical systems vendors to survive, so the potential implications are very meaningful,” he says.

Equally, MKM Partners views the acquisition as a positive development for the few large optical systems companies that make their own DSPs: “The reason is that the Tier 2 and Tier 3 vendors are likely to be severely weakened, and the overall industry structure should improve in favour of the large leaders.”

Others view Acacia becoming part of Cisco less bleakly.

ADVA says such a development is to be expected. “As the world becomes more open and disaggregated, it is only normal and necessary that the supplier-customer relationships in our ecosystem evolve,” says Stephan Rettenberger, senior vice president, marketing and investor relations at ADVA. “The formerly clean delineation between component houses and system vendors has started to blur.”

Vladimir Kozlov, LightCounting

Rettenberger points out that with companies such as NEL and Inphi, there are still merchant DSP experts supplying the market.

Kozlov also expects the merchant DSP market to recover: “Inphi is committed to it, NEL may get more business, and new vendors may enter including start-ups like Wingcomm.”

Cisco intends to run Acacia as a component business unit and will continue to sell to all equipment makers, says ADVA’s Rettenberger, while Ciena’s Optical Microsystems unit is making its WaveLogic coherent DSPs and module technologies available to the wider market.

“We at ADVA also run an in-house component team to be more vertically integrated and differentiated at a systems level,” says Rettenberger.

That said, system vendors that work closely with Acacia, share their upcoming systems designs and are privy to Acacia’s coherent product roadmap may have reservations working with Cisco post-deal. “I think we have to assure Acacia’s customers that their information will be protected; that is critical,” says Johnson.

Genovese also questions whether long-term Cisco will support Acacia’s customers. “These optical components companies [that Cisco has acquired] tend to disappear inside of Cisco and become features on Cisco products, rather than stay ongoing merchant optical component vendors,” says Genovese in a research note.

Johnson counters by pointing out how Acacia’s strong and open culture underpins its success. “Spending this type of money and disrupting that, and not allowing them to execute as they have; that would be a really bad thing for Cisco to do,” he says.

Acquisition history

The announced deal is Cisco’s second significant optical move in recent months after completing the acquisition of silicon photonics module maker, Luxtera, in February.

Cisco has been down a similar acquisition path before, acquiring coherent technology firm CoreOptics and silicon photonics player, LightWire. But while the acquisitions have served Cisco - LightWire enabled Cisco to come to market with its 100-gigabit CPAK to feed its switch ASIC one year ahead of the competition, while CoreOptics enabled Cisco to have its own early-generation coherent DSPs - the acquisitions no longer serve all Cisco’s needs.

Which is why, with the growing importance of high-speed optics and silicon photonics within the data centre, and the move of coherent optics from chassis-based platforms to pluggables, Cisco is reopening its chequebook.

According to Johnson, Cisco’s LightWire team has not been focused on making products since the CPAK but rather has been building a library of capabilities that will be used to build products.

“What they have been doing is a series of design experiments to prove out different functions of the optics, specifically grey optics, to go after the promise of silicon photonics,” he says. This includes wafer-scale integration and wafer-scale testing. When LightWire was acquired, these aspects of silicon photonics were not developed.

On completion of the deal, Cisco can couple its own LightWire and Luxtera silicon photonics expertise with Acacia’s.

“Even with all three, we still don’t have the critical mass to go after all of the different silicon photonics opportunities,” says Johnson. “In almost every piece of work that we define and go after, from a requirements perspective and a market perspective, the confining thing is the resource we have to make it all happen.”

Ideally, Cisco would have invested in its LightWire and CoreOptics acquisition and achieved all of the success that Acacia has had without having to invest $2.6 billion, admits Johnson.

“We fell behind with the DSP technology,” he says. And while Cisco could have invested much more to try and outpace the likes of Acacia and Ciena, he doubts it would have been successful.

Meanwhile, Acacia has been able to engage the broader industry and make products that fit more applications: “Cisco and all of Acacia’s customers have benefitted from that,” says Johnson.

Now, Cisco wants to more exclusively benefit from Acacia and is willing to spend big to do so.

WaveLogic 5: Packing a suitcase of ideas in 7nm CMOS

-

Ciena’s WaveLogic 5 coherent digital signal processor family comprises the Extreme and Nano chips

-

The WaveLogic 5 Extreme maximises optical capacity and transmission reach while the WaveLogic 5 Nano is targeted at compact, power-conservative applications

Kim Roberts

Advancing coherent optical transmission performance; targeting the emerging coherent pluggable market; selling modules directly, and the importance of being more vertically integrated. All these aspects were outlined by Cisco to explain why it intends to buy the coherent optical transmission specialist, Acacia Communications; a deal that is set to be completed in the spring of 2020.

But such strategic thinking is being pursued by Ciena with its next-generation WaveLogic 5 family of coherent DSPs.

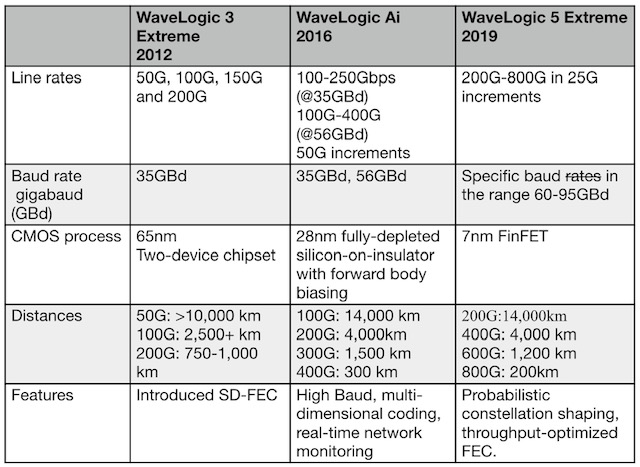

The WaveLogic 5 continues Ciena’s tradition of issuing a coherent digital signal processor (DSP) family approximately every three years: Ciena announced the WaveLogic 3 in 2012 and the WaveLogic Ai in 2016. (Add links).

The company has managed to maintain its three-yearly cadence despite the increasing sophistication of each generation of coherent DSP. For example, the WaveLogic 5 Extreme will support 800 gigabits-per-wavelength, double Ciena’s WaveLogic Ai that has been shipping for nearly two years.

Kim Roberts, vice president of WaveLogic science, says Ciena has managed to deliver its coherent DSPs in a timely manner since much of the algorithmic development work was done 5-6 years ago. The issue has been that certain features developed back then could not be included within the WaveLogic Ai.

WaveLogic 5 is implemented using a 7nm FinFET CMOS process whereas the WaveLogic Ai uses a 28nm specialist CMOS process known as fully-depleted silicon-on-insulator (FD-SOI).

“Seven-nanometer CMOS, due to its density and low heat, allows us to implement things that didn’t make the cut for the WaveLogic Ai,” says Roberts.

The company has a ‘suitcase of ideas’, he says, but not all of the concepts make it into any one generation of chip. “They have to justify performance versus schedule versus heat [generated],” says Roberts. “As we improve the technology, more features make the cut.”

And there are developments that will be included in future designs: “We keep refilling the suitcase,” says Roberts.

NAMING

Ciena first used the Extreme and Nano nomenclature with the WaveLogic 3. In contrast, the WaveLogic Ai, when launched in 2016, was a single-chip targeting the high-end. Ciena chose to change the naming scheme with the Ai since the chip signified a shift with features such as network monitoring.

However, Ciena highlights a key difference between the WaveLogic 3 and WaveLogic 5 families. The WaveLogic 3 Extreme and the WaveLogic 3 Nano could talk to each other on appropriate spans. In contrast, the two WaveLogic 5 chips are distinct. “They are not designed to interwork,” says Roberts.

NETWORKING TRENDS

Telecom service providers are investing in their networks to make them more adaptive. They want their networks to be scalable and programmable, says Ciena.

The operators also want to better understand what is happening in their networks and that requires collecting data, performing analytics and using software to configure their networks in an automated way.

“How do you get there? It is all about coherent technology,” says Helen Xenos, senior director, portfolio marketing at Ciena. “It is a critical element that is helping operators scale their networks.”

By enhancing the traffic-carrying capacity of fibre, coherent technology enables operators to reduce transport costs. “It allows them to be more competitive as they can do more with the hardware they deploy,” says Xenos.

Helen Xenos

Both telcos and cable operators are also applying coherent technology to new applications in their networks such as access.

These transport needs are causing a divergence in requirements.

One is to keep advancing optical performance in terms of the spectral efficiency and the traffic-carrying capacity of links. This is what the WaveLogic 5 Extreme tackles.

The second requirement - producing a compact coherent design for the network edge - is addressed by the WaveLogic 5 Nano.

For access designs, what is important is a compact design where the optics and the DSP can operate over an extended temperature range.

The Nano also addresses the hyperscalers’ need to connect their distributed data centres across a metro. “They need high capacity - 400 gigabits - and short-reach connectivity,” says Xenos. “It really needs to be the smallest footprint to maximise density.”

VERTICAL INTEGRATION

In addition to unveiling the WaveLogic 5 Extreme and Nano ICs, Ciena has outlined how it is more vertically integrated after investing in optics. In 2016, Ciena acquired the high-speed photonics division of Teraxion, gaining expertise in indium phosphide and silicon photonics expertise. {add link}.

Ciena is also now selling coherent optical modules. Gazettabyte revealed last year that Ciena was planning to sell modules using its own optics and WaveLogic technologies. {add link}

The company has no preference regarding indium phosphide and silicon photonics and uses what is best for a particular design.

“Silicon photonics buys you ease-of-manufacturing and cost; indium phosphide is what you need for 800 gigabits,” says Xenos.

Ciena stresses, however, that there is no simple formula as to when each is preferred. In terms of size and heat, silicon photonics has a strong advantage. “In terms of performance, you get better performance in some instances with indium phosphide and then there are overlaps because you bring in cost and other constraints,” says Roberts. “So there is no simple divide.”

“As we move forward, we are going to see an increasing percent of Ciena-custom components in WaveLogic coherent modems,” says Xenos.

Source: Gazettabyte

EXTREME

The WaveLogic 5 Extreme introduces several developments. It operates at specific baud rates ranging from 60 to 95 gigabaud. The baud rates are chosen so that both fixed-grid 100GHz channels and flexible grid ones are supported.

“For the best performance, you have flexible grid when 95 gigabaud is the primary baud rate,” says Roberts.

It is also Ciena’s first coherent DSP that uses probabilistic constellation shaping, a coding scheme used to achieve granular capacity increments. {add link}

“From 200 gigabits to 800 gigabits [in 25-gigabit increments], optimised over any path or the available margin,” says Roberts. “But what is unique about this is that it is optimised for non-linear propagation.”

Initially, the products using the WaveLogic 5 Extreme will use 50-gigabit increments. “This is what is required to service customers’ client requirements today: ten gigabits and multiples of 100-gigabit clients,” says Xenos.

>

“With 25-gigabit steps in client rate, the customer can choose to spend the margin on sending more bits”

The DSP uses four-wave frequency-division multiplexing to mitigate non-linear impairments, particularly beneficial for sub-sea systems.

Ciena says the four-wave frequency-division multiplexing is achieved electrically, reducing the optics to a minimum. “One laser and one modulator are used, so all the [cost-saving] economics of a single optical wavelength,” says Roberts. “But it has the non-linear performance of four tightly-coupled electrical systems.”

Ciena has also added an improved forward-error correction (FEC) scheme - a ‘throughput-optimised FEC’ - that uses variable overhead bits depending on the client rate.

“It will handle 8.6 percent errors compared to what we used in the WaveLogic Ai which handles 3.5 percent errors,” says Roberts. “So it is a decibel better.”

The Extreme chip also has improved link-monitoring capabilities. It monitors the signal-to-noise per channel as well as quantifies the non-linear contributions. “It helps people to understand what is happening in the network and create algorithms to optimise the capacity across the network,” says Xenos.

PROBABILISTIC CONSTELLATION SHAPING

Probabilistic shaping is used to improve the optical performance by lowering the signal energy by not using all the constellation points. Unless, that is, the full data rate is used and then all the constellation points are needed.

The degree of probabilistic shaping used is determined for each link. The parameters used to determine the probabilistic shaping are the amount of dispersion on the link, the span’s reach, and the transmitted client rate.

“The modem will measure what is going on in the link and the customer or some higher-level software will say what the client rate is,” says Roberts. “The modem will then figure out how to do the best non-linear probabilistic shaping to support that rate on the link.”

Roberts says other firms’ probabilistic shaping use one symbol at a time whereas Ciena use blocks, each comprising 128 symbols. “A bigger number would be better but I'm limited by my hardware,” says Roberts.

The 128 symbols equate to 1024 bits: four magnitude bits using 64-ary quadrature amplitude modulation (64-QAM) multiplied by two, one for each polarisation.

This means there are a total of 2^1024 combinations of 1024-bit sequences that could be sent. However, when sending a 400 Gigabit Ethernet (GbE) client signaland, for the benefit of explanation, assuming that 555 bits are needed to carry the data payload and the overhead, the number of possible bit sequences is trimmed to 2^555.

This is still a fantastically huge number but the DSP can work out which are the best 555-bit sequences to send based on them having the most tolerance to linear and non-linear interference.

“The ones that play nicely with their neighbours such that they cause the minimum non-linear degradation on the neighbouring wavelengths and on the other symbols,” explains Roberts.

Ciena is not forthcoming as to how it calculates the best sequences. “Ciena’s algorithms decide which ones are best,” says Xenos. “This is one of our key differentiators.”

The result is that, depending on the fibre type, a 1.5dB performance improvement is achieved for the non-linear characteristics.

“It allows more capacity to be chosen by the customer on that same link,” says Roberts. “With 25-gigabit steps in client rate, the customer can choose to spend the margin on sending more bits.”

Operating the Extreme at 95GBd, a reach of 4,000 km is possible at 400 gigabits and at 600 gigabits, the reach is 1,000 km (see table).

WAVELOGIC 5 NANO

The WaveLogic Nano supports 100-gigabit to 400-gigabit wavelengths and is aimed at applications that need compact designs that generate the least heat.

One application is to enable cable operators to move optics closer to the user and that must operate over an extended temperature range. Here, a packet platform is used that will support line interworking as equipment from different vendors may be at each end of the link.

Another requirement is operating over multiple spans in a metro. Here, compact equipment and low power are more important than spectral efficiency but it is still a challenging environment, says Ciena. Hundreds of nodes may be talking to each other and there may be cascaded reconfigurable optical add-drop multiplexers (ROADMs) with different fibre types making up the network.

A third application is single-span data centre interconnect where achieving the highest density on routers is key. This is the application the 400-gigabit, at least 80km 400ZR specification developed by the Open Internetworking Forum will address.

“The design that we are doing for the WaveLogic 5 Nano for 400ZR is to fit into a QSFP-DD,” says Xenos. “If there is a need for an OSFP [pluggable module], we will offer OSFP.”

Ciena also expects to offer a Nano-based CFP2-DCO module, which will outperform the ZR in terms of reach and features, for more demanding metro applications.

Another new segment requiring coherent optics is 4G and 5G access. “It is to be determined what type of platform is the winning solution in this environment,” says Xenos.

MAKING MODULES

Ciena first made its coherent DSP available to third parties in 2017 when it signed an agreement with Lumentum, NeoPhotonics and at the time Oclaro (since acquired by Lumentum) to use its WaveLogic Ai in their modules.

Now Ciena is selling directly the full coherent modem: the DSP and the optics. This is why Ciena created its Optical Microsystems unit in late 2017.

CMOS PROCESS

Moving to a 7nm FinFET CMOS process delivers several benefits.

It generates much lower heat than the WaveLogic Ai’s 28nm FD-SOI process. It also has a lower quiescent current, the current dissipated independent of whether the chip’s logic is active or not. And 7nm CMOS delivers much greater circuit density: the functionality that can be crammed into a square micrometre of silicon.

“So, a low power [consumption] on features you are not using, and we can include features that if you can't afford the heat, you can turn them off,” says Roberts.

It will offer its Nano in the form of pluggable modules, the WaveLogic Ai as a 5x7-inch module, and the WaveLogic 5 Extreme in another module form factor that will have its own interface. “These would all be viable optics,” says Xenos.

Availability

The first Wave Logic 5 Nano products will appear in the second half of this year while the first Extreme-based products will be available at the end of this year. The 400ZR coherent pluggable module is expected to be available in the first half of 2020.

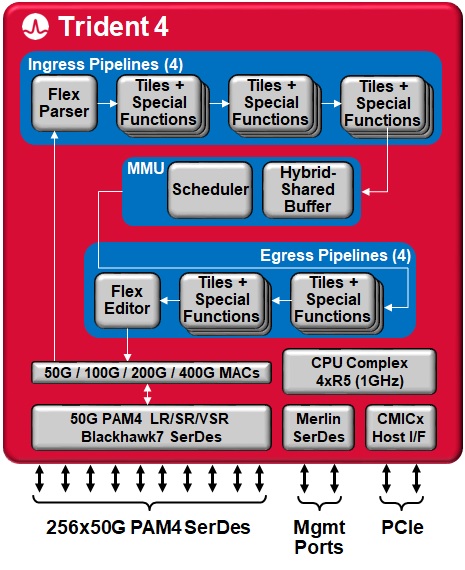

Trident 4 boosts enterprise switch capacity to 12.8 terabits

-

Broadcom’s Trident 4 switch chip has a capacity of 12.8 terabits, 4x the capacity of its Trident 3.

-

The chip reduces fourfold the cost of a 128x100-gigabit switch.

-

The Trident 4 adds compiler programmability

-

This is the company’s first switch chip in 7nm CMOS

Broadcom has unveiled the Trident 4, its latest family of switch chips for the enterprise.

The largest-capacity Trident 4 family member, the X11 chip, has a switching capacity of 12.8 terabits. This is a fourfold increase in capacity compared to Broadcom’s current high-end enterprise chip, the Trident 3, announced in June 2017.

Peter Del Vecchio

The Trident 4 will also reduce the cost of a 128x100-gigabit switch by a factor of four. The current cost of a 12.8-terabit switch, a multi-chassis solution, is $245,000 not including the pluggable optics, says Broadcom, citing market research firm, The Dell’Oro Group.

“The announcement is significant both in updating the Trident line for enterprise and in adding compiler programmability thereby limiting the openings for competitors such as Barefoot - soon Intel - Innovium, and Marvell,” says Bob Wheeler, vice president of The Linley Group and principal analyst for networking.

The X11 matches the capacity of Broadcom’s leading Tomahawk 3 switch chip used by the hyperscalers in their data centres.

“With the Tomahawk line, the goal is always to lead in terms of bandwidth as far as gigabits-per-second/ Watt,” says Peter Del Vecchio, product line manager for the Trident 4 at Broadcom.

In contrast, enterprises need to support a variety of networking protocols so that while the Tomahawk is a streamlined design, the Trident family requires a broader feature set.

“The Tomahawk 3 was Broadcom’s first 12.8-terabit chip and we were able to achieve that in 16nm CMOS,” says Del Vecchio. “To achieve 12.8 terabits in a monolithic implementation with Trident class functionality, we moved to 7nm."

Trident 4 programmability

The first 12.8-terabit Trident 4 chip has been in the hands of customers since May.

Broadcom will offer a family of Trident 4 devices. The company is starting at the high-end with its 12.8-terabit X11 and 8-terabit X9 and will offer subsequently the 4-terabit X4 and 2-terabit X3 devices.

“Trident 4 matches the bandwidth of the Barefoot Tofino 2, Innovium Teralynx, and Marvell Falcon,” says Wheeler. “That is overkill for many enterprise applications, which is why Broadcom will offer lower bandwidth variants, as Marvell does.”

The company has also enhanced the switch-chip programmability with the Trident 4.

Many Trident 3 customers see it as a fixed-function chip and use the features provided by Broadcom.

Trident 3, while programmable, does not come with a compiler. it requires Broadcom’s engineers to handcraft the images that go into the device’s programmable elements. Broadcom thus provides the software-image upgrades that are implemented in the field.

“We take input from customers that have an evolving roadmap and add features to the Trident 3 line,” says Del Vecchio.

For the Trident 4, Broadcom has developed a compiler suite and is making available the source code for the base images used for the device. Switch vendors and enterprises can use the compiler to tweak the source code to add proprietary features and differentiate their applications.

“Programmability also provides future-proofing for both OEMs and end customers, extending the life of Trident 4-based systems,” says Wheeler.

Broadcom uses its high-level Network Programming Language (NPL) to program the Trident 4 and has made available the language’s specification. It is also open-sourcing the front-end compiler and a behavioural simulator.

>

“The Tomahawk 3 was Broadcom’s first 12.8-terabit chip and we were able to achieve that in 16nm CMOS. To achieve 12.8 terabits in a monolithic implementation with Trident class functionality, we moved to 7nm.”

P4 and NPL

There is already an open-source programming language for switch silicon, dubbed P4, overseen by the Open Networking Foundation (ONF).

Broadcom says that its NPL language is not competing with P4. “We have participated in P4 and have given a lot of detail as to what we have in NPL,” says Del Vecchio. “Our hope is that the industry eventually converges.”

However, the limitations of the P4 language means that the company cannot wait for the open community to adopt everything it needs to get Trident 4 to market, says Del Vecchio, who stresses that switch makers choose their chips based on bandwidth, efficiency and protocol support, not the language used for the chip’s coding.

“This is not something where you have millions of lines of code,” says Del Vecchio. “If someone wants a priority feature, like a tweak to a header format, they tackle the existing stack and code a few tens of lines.”

Images and code migration

The main image that customers will use with the Trident 4 is the Datacenter NPL Application (DNA). This application supports a comprehensive set of protocols similar to Trident 3, with added features available with the Trident 4.

Broadcom also includes additional Trident 4 applications including support for large-scale network address translation (NAT), load-balancing, and distributed denial-of-service (DDoS) protection.

But Del Vecchio says that the DNA image will meet most customers’ needs whether for data centre use cases and for general enterprise networking.

Broadcom has also developed a legacy application programming interface (API) mapping layer to its compiler code to aid migration of Trident 3 software to the Trident 4 (see diagram below).

The API mapping layer translates legacy APIs used for the Trident 3 into logical table-based calls, what Broadcom calls its Software Development Kit Logical Table (SDKLT) APIs.

Logical tables are used to expose the switch’s information such as MAC addresses, layer 3 route tables and the device’s ternary content-addressable memory (TCAM). The switch chip’s behaviour is managed by accessing these logical tables via the APIs.

The network operating system (network OS) shown in the diagram is used to control the switch in real-time, using the functionality defined in the NPL code. The API mapping layer generates the APIs needed for the network OS to control the Trident 4.

Source: Broadcom

Instrumentation

The Trident 4 includes enhanced instrumentation that is used to collect data to understand how the chip and the network are behaving.

“There is no defacto standard [regarding instrumentation],” says Del Vecchio. Broadcom, therefore, supports two approaches: in-band telemetry and streaming telemetry.

With in-band telemetry, information - metadata - is added to a packet as it passes through the network. Once the packet arrives at the endpoint - which can be a switch, a network interface card or a hypervisor - the metadata is stripped off to understand what happened to the packet on each of its hops in the network.

With streaming telemetry, in contrast, the switch chip collects statistics regarding latency, queue levels and the state of congestion, which are sent to a ‘collector’.

“Some companies want one [approach] more than the other,” says Del Vecchio. “With the Trident 4, we do both.”

Broadcom has also added real-time programmability to the Trident 4 that allows device changes on-the-fly.

“Now you can tweak things in the network, be it instrumentation or packet flow, and you don’t have to wait for the switch to come down for the upgrade,” says Del Vecchio.

The capability can be used to modify the switch’s behaviour without packet loss. For example, if a DDoS attack is suspected, or the real-time programmability can be used to tune applications and the network.

Broadcom stresses that the Trident 4 is a monolithic die whereas other 12.8-terabit chips announced by competitors, such as the Barefoot Tofino 2 and the Marvell Falcon, are a multi-chip design comprising a main die and chiplets that support the input-output.

Monolithic versus a multi-chip design

A monolithic chip has advantages in terms of time-to-market in that there is no interposer to debug, less total silicon area as there is no need for ASIC-chiplet interfaces, claims Del Vecchio. That said, Broadcom does agree that the use of chiplets is where switch design is going and is an approach Broadcom is investigating.

“All else being equal, such as memories, etc., we believe a monolithic die will offer the lowest power and the lowest cost,” says Wheeler.

Switch pipeline

The Trident 4’s packet-processing pipeline comprises input (ingress) and output (egress) paths (see chip diagram above).

“With the Trident 4, you do have the flexibility where you can take resources in the pipeline and tie them to a separate set of features,” says Del Vecchio. “With other architectures, you might not be able to do that and also support a full protocol stack.”

The Trident 4 uses what Broadcom calls a tile-based architecture.

Three tile types are used: Hash tiles, Index tile and TCAM tiles, the names referring to the tile’s memory and how it is accessed. Hash and Index tiles’ table state being held in SRAM while the latter uses TCAM.

“For Hash tiles, the SRAM access is performed using a hash computation,” says Del Vecchio. “For the Index and TCAM tiles, the access is a direct lookup into the table state.”

The tile is where a look-up table resides and where the programmable key generation and programmable policy reside. The key is used to access the SRAM or TCAM, says Del Vecchio. It is generated using the tile's key-generation logic with the function performed by the logic being specified by a user's NPL program. “The inputs to that function are packet fields or metadata from previous pipeline stages,” says Del Vecchio.

Meanwhile, a tile’s policy can dictate when a packet is dropped, traced, mirrored, modified of has its forwarding changed.

The Trident 4’s pipeline also includes special-function hardware engines that operate at line rate. These are used for common networking applications such as quality of service, equal-cost multi-path (ECMP) load balancing, and hash computations.

“We also have a special function which we call flex switch logic that allows you do optimised arithmetic such as Boolean applications and weight-based decisions,” says Del Vecchio. “The special functions and the flex switch logic is what makes the Trident 4 differentiated from other programmable architectures.”

The Trident 4 also has 256 serialiser/ deserialisers (serdes), each running at 50 gigabits-per-second (Gbps), similar to its Tomahawk 3. The Trident 4 is also pin-compatible with the Tomahawk 3, minimising the switch-making development effort.

LightCounting Market Research expects to see 128-port 100GbE switches with a single Trident 4 ASIC. Indeed, Broadcom expects the first Trident 4-based systems to be available as early as the year-end or the first quarter of 2020.

The largest enterprises will be able to move to 200 Gigabit Ethernet (GbE) or 400GbE whenever they wish. All this bodes well for sales of 100-gigabit and faster Ethernet optical module, says LightCounting.

UK quantum algorithm start-up identifies promising opportunity

A UK start-up developing software for quantum computers has received £3.25 million ($4.1 million) in funding.

Riverlane, based in Cambridge, is working with leading quantum computing hardware companies as well as large corporates interested in benefiting from the technology.

The start-up will use the funding to grow the company and has already identified the most promising applications for the technology.

“A lot of people are building hardware using various technologies such as iron trap or supercomputing qubits,” says Steve Brierley, CEO of Riverlane. “What we are trying to do is make that [hardware] useful as soon as possible.” A qubit is the shorthand term for a quantum bit.

Riverline’s core expertise is quantum-computing algorithms and its goal is to demonstrate quantum computing in high-value applications.

“Some of our techniques are orders of magnitude faster than existing quantum software,” says Brierley. “We take the same quantum computer but it runs ten times or one hundred times faster.”

Quantum computing

Riverlane’s focus is to work with circuit-based quantum computers. Such quantum computers are capable of solving any type of problem including those where there is no advantage using such technology in preference to classical computers. “That would be an expensive way of solving classical problems,” says Brierley.

But the great interest in quantum computing is its ability to solve certain problems that are beyond the capabilities of classical computing. Riverlane’s focus is to identify what it says are $1 million computational problems where quantum computing outperforms CPU-based platforms.

One early task the start-up undertook was working through key quantum algorithms and identifying the associated industry applications. “How big a quantum computer would you need to run that calculation and how valuable would the results be,” says Brierley.

The undertaking helped the start-up develop a roadmap for quantum computing.

One large application area is the factoring of very large numbers that can be used to break cryptosecurity systems. Such an application area is coming but maybe 10-15 years in the future, says Brierley.

Other applications include solving optimisation and scheduling problems. Here, Riverlane can estimate how big a quantum computer - measured in the number of qubits - is needed to outperform high-performance computing.

>

“One application area that stands out from all the computational problems Riverlane has investigated is computational chemistry”

Focus

One application area that stands out from all the computational problems Riverlane has investigated is computational chemistry, a discipline that can be used to model new materials for battery technology and solar cells, and protein-drug interactions for the discovery of medicines.

“Essentially what we are doing is modelling physics at the molecular level,” says Brierley. “And the reason quantum computers are so good at that is that they themselves are quantum machines.”

In this context, a quantum computer can be viewed as an atomic system that is controllable, modelling some other atomic system. This is a class of problem where quantum computers shine and are exponentially better at solving than traditional computers.

Brierley also cites the example of the Haber-Bosch process used to make fertiliser for food production. This, he says, is an extremely energy-inefficient process that accounts for some two percent of the world’s energy consumption. In contrast, nature has its own nitrogen-fixing process that is performed at room temperature and requires almost no energy.

“So there exists a process, we just don’t know what it is,” he says. “Modelling that process is a way to develop a new industrial process for production fertiliser.”

Some five years ago, the size of quantum computer thought necessary to model such a problem required billions of qubits, says Brierley. Such a large machine will be possible in the future but represents a hugely challenging problem.

“But through better algorithms and software, we are now down to solving that same problem with millions of qubits and I see us continuing that trend,” says Brierley.

Once the problem can be reduced to requiring several hundreds of thousands of qubits to solve, practical systems ‘just might be possible’ in the next decade, he says.

>

“Essentially what we are doing is modelling physics at the molecular level. And the reason quantum computers are so good at that is that they themselves are quantum machines.”

Quantum hardware

Companies developing quantum computing hardware, the likes of IBM, Google and Intel, have systems but they are small-scale, says Brierley: “They are pushing this technology along but no one is claiming they have got a quantum computing.”

The challenge facing the industry is scaling such systems. Twenty-qubit devices are generally available and next-generation 128-qubit devices are on the hardware companies’ roadmaps.

“The mid-term ambition is to get to 1,000 qubits and in five years’ time you will see multiple companies with thousands of physical qubits,” says Brierley. But he points out that such devices are still ‘noisy’. “If you could produce perfect qubits without any noise, 1000 would be a huge number,” he says.

And while there are quantum error-correction schemes being developed, the issue of noise is pushing out the time frame of quantum computing.

Riverlane is working with hardware companies such as Google and IBM but has yet to announce the end-user companies that it is partnering with. The typical engagements are with the R&D departments of large multinationals that want to understand the new technology and how it will benefit their research.

“I think what you will see next is one of the great quantum hardware companies showing off their technology but it will be running our software,” says Brierley. “And it will be achieving more because it is running our software.”

Venture funding

Riverlane says it will use the seed funding to grow the company. The goal is to recruit between 20 and 25 staff by the end of 2020. Riverlane’s staff will number 14 by September.

The start-up is seeking mathematicians, physicists, computer scientists and computational chemists.

One challenge is to ensure employees communicate with one another.

“We all come from different fields and one of the most important things we have done as a company is how we all work on the same problem,” he says.

Brierley says securing the funding was relatively straightforward. “The most important thing was to find the right match with the investors that would see the potential of the company and understand the timescales,” he says. The key was finding such partners.

The venture capital investors in Riverlane are Cambridge Innovation Capital and Amadeus Capital Partners. Cambridge Enterprise, a wholly-owned subsidiary of the University of Cambridge, is another backer.

Sense and sustainability

What causes someone to change roles, to turn to sustainability after years as a distinguished engineer? An interview with Klaus Grobe of ADVA; the second in a series of articles about work.

Klaus Grobe spent nine productive years as part of the Advanced Technology team at ADVA.

Grobe had authored 150 academic papers, issued 25 patents, and had published, along with co-author Michael Eiselt, a textbook on wavelength division multiplexing (WDM) when, in 2015, he decided to switch roles and become ADVA’s director of sustainability.

Two factors influenced his decision: one was the importance he attached to the topic of carbon emissions and global warming, the second was a sense that it was time for a change.

“I wouldn’t go so far as to say that being a technologist had become boring but it wasn’t that exciting anymore,” says Grobe. “I was looking for something new and perhaps more relevant.”

At the time, a position had opened up at ADVA to head its sustainability programme after the company recognised it needed to do more. Grobe put himself forward and was appointed.

Grobe answers straightforwardly why he refers to sustainability as more relevant. “Do I understand and believe what is going on with the term climate change? Am I a denialist or not?” he says. “And if I’m not, it is very clear that these things are more relevant because they are a prerequisite for everything else.”

WDM book

Grobe co-authored the WDM textbook after contributing a chapter on the topic for two editions of a book on fibre-optic data communication.

The resulting book, Wavelength Division Multiplexing: A Practical Engineering Guide, published in 2013, involves quite a bit of maths; one page includes an equation with a quintuple integral.

Grobe says that while he didn't use that much maths in his role as a technologist, he was familiar with the maths needed to understand the many references included in the book due to his doctoral work.

“I'm not sure I'd do it again [writing a book] if I’d known the effort required,” says Grobe.

The book, however, did deepen his overall understanding. “If you want to go into a certain level of detail regarding a topic, write a book about it,” he says.

>

“Do I understand and believe what is going on with the term climate change? Am I a denialist or not? And if I’m not, it is very clear that these things are more relevant because they are a prerequisite for everything else”

Changing roles

“From a purely mathematical point of view, I could argue my PhD was on the topic of non-linear processes,” says Grobe, adding that the majority of people don’t understand the effect of non-linearity and in particular exponential non-linear processes. “And here we are, exactly in the middle of one [such process],” he says.

Currently, humanity is experiencing what he says is the very steep part of the curve of emission-increasing carbon dioxide. “And there are other non-linear growth processes going on as well,” he says.

Grobe says that at the time of his role change, ADVA was being pushed by its operator customers to do more in the area of sustainability. It also became clear to ADVA that a new company organisation was needed that would report to the senior management of the company, the CxOs.

Sustainability model

Sustainability for a telecom systems vendor covers many company aspects besides issues such as carbon emissions and product recycling.

ADVA first adopted a sustainability model developed by telecom operator BT and later from the QuEST Forum, a global organisation that addresses sustainability in the information and communications technology (ICT) segment.

The QuEST Forum is known for its TL-9000 quality management practice for the ICT segment, and in 2017 it merged with the Telecommunications Industry Association (TIA).

“BT, the QuEST Forum and the TIA developed and use this [sustainability] model which covers ten segments,” says Grobe (see diagram).

Source: TIA

Broad scope

One model category is emissions and is known as the carbon dioxide footprint. Another is resource efficiency optimisation that holds for products and also production processes, says Grobe. A third category - environment management certification - includes meeting a family of standards that make up ISO 14001 qualification. Another qualification standard Grobe mentions is energy management, ISO 15001.

Then there are categories that, at first sight, are harder to grasp such as the circular economy lifecycle and stakeholder engagement.

The circular economy is a vehicle aimed at decoupling commercial or business growth from resource usage.