The OIF has a range of demonstrations lined up for this week’s OFC show in Los Angeles.

-

448-gigabit electrical interconnect, and vendors showing more module offerings and interoperability at 224-gigabit electrical signalling.

-

Coherent optics: 800-gigabit pluggable modules operating over the L-band.

-

The first multi-core fibre modules that are part of an OIF OFC demo: 800G DR, and coherent ZR sent over multi-core fibre.

CEI-448G steps into view

A main OFC showpiece will be a live 448 gigabit-per-second (Gbps) electrical signalling demonstration, part of the OIF’s Common Electrical Interface specification work (CEI-448G).

The goal is to showcase 448-gigabit electrical transmissions using advanced test-and-measurement gear and 448-gigabit silicon.

The test and measurement equipment for 448 gigabit is huge, power-hungry, and noisy, whereas the 448-gigabit silicon uses the latest CMOS process node and is tiny.

“It is like a refrigerator versus a penny, and they’re both doing the same thing,” says Mike Klempa, the OIF Physical and Link Layer (PLL) Interoperability Working Group Chair, and of Qualcomm (Alphawave Semi).

The 448-gigabit demo will showcase different signalling options, including PAM4, PAM6, and PAM8, along with measurements such as bit-error rates and eye diagrams.

At 224 gigabits, the demos will emphasise the ecosystem’s broadening and growing maturity. The emphasis is on growing interoperability across a range of implementations: silicon, modules, linear-drive pluggable optics, direct-attach copper (DAC) cable, active copper cable (ACC), and retimed and unretimed approaches.

Coherent optics, L-band and multi-core fibre

For the OIF’s 800-gigabit coherent optics interoperability demonstration, a notable addition will be support for the L-band for the first time.

Multi-core fibre will also be part of the demos.

“We will also use the multi-core fibre in one of our [coherent] ZR links,” says Karl Gass, OIF Physical & Link Layer Working Group Optical Vice Chair, another first.

In turn, 800-gigabit DR (Data Centre Reach) intensity-modulation direct-detection (IMDD) transmission will be shown working across multi-core fibre.

The OIF does not define multi-core fibre but hyperscaler interest means it will be part of the OIF demonstrations.

First CEI-448G projects now underway

The OIF has also announced that it has kicked off the first two CEI-448G specification projects: 448-gigabit very short reach (VSR) and long-reach (LR) interfaces.

“We have officially started work, but we have not got to where we are defining specific parameters, like loss budgets, modulations, and jitter targets,” says Nathan Tracy, OIF President and Technologist, System Architecture Team at TE Connectivity.

The VSR interface refers to the chip-to-optical-module link that spans anywhere on the host board to a chassis faceplate. Or as Tracy puts it: “Getting the signal out of the box.”

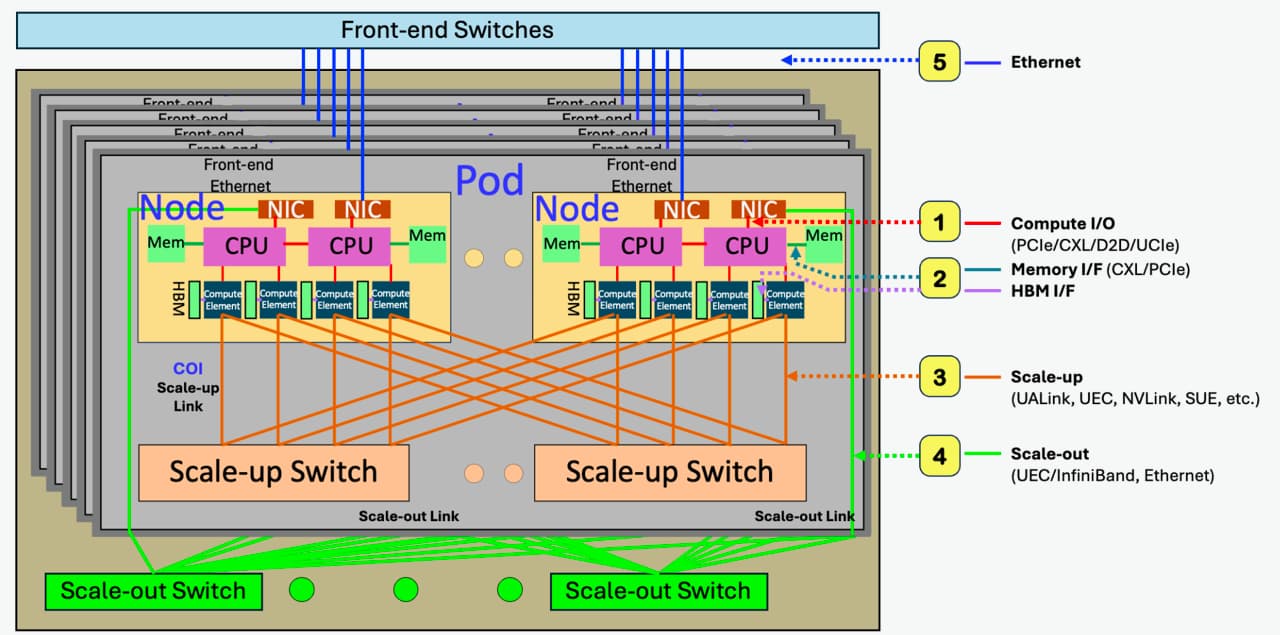

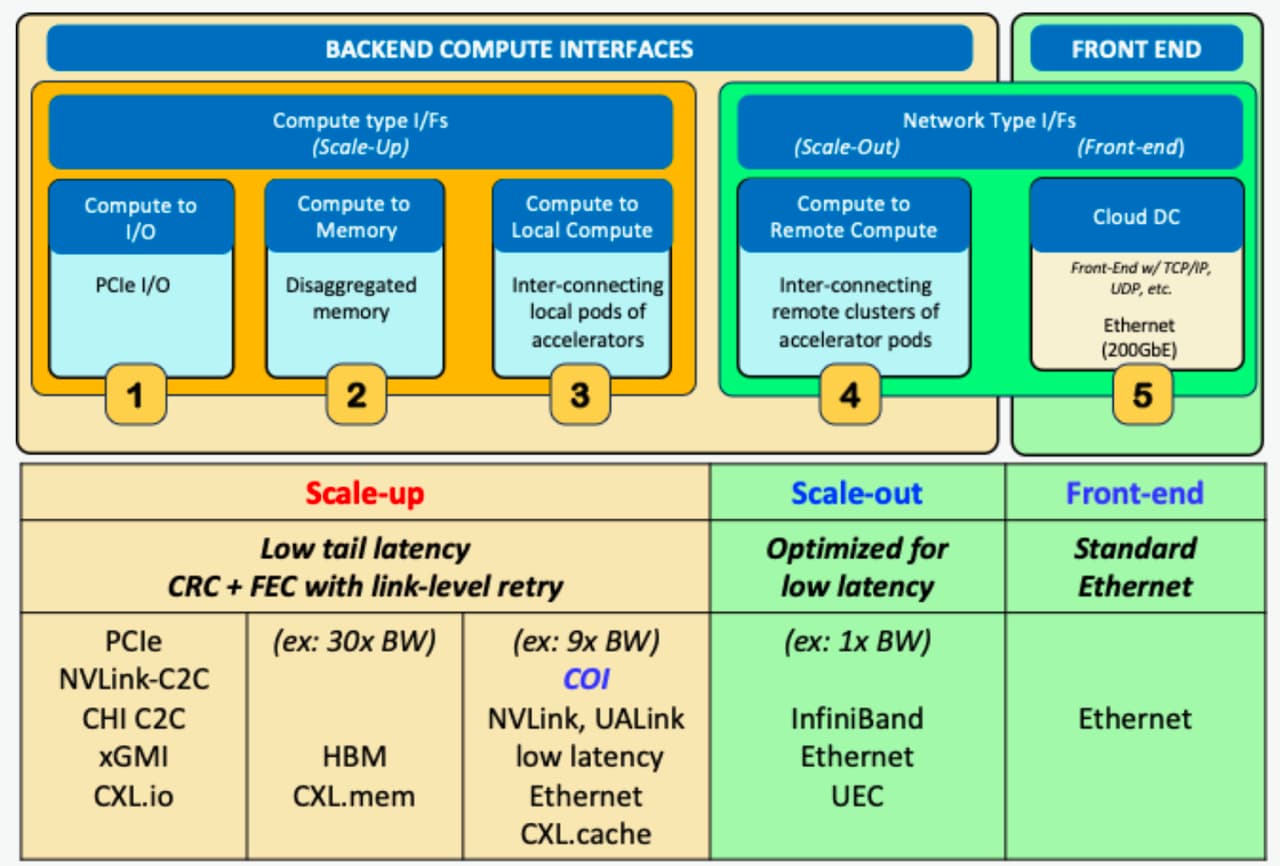

The LR interface refers to the link between line cards via a rack’s backplane and even between racks. In AI architectures, this is referred to as the scale-up architecture.

“LR needs to be at least one meter, but we’re fighting with all these extra package losses and higher insertion loss channels, and that is challenging,” says Klempa, adding that CEI-448G LR will require additional techniques and tools compared to what is used for CEI-224G LR.

White papers aim to narrow the design space

The OIF has also recently published two White Papers. One details the OIF’s energy-efficient interfaces; a framework for categorising the interface types.

The second White Paper, a 50-page document, is titled “Compute Optics Interface (COI): Energy-Efficient Photonic Interconnects for AI Compute Scale-up.”

The purpose of the documents is to guide the industry in identifying more energy-efficient hardware architecture solutions for AI clusters. The OIF also wants feedback to inform its future specification work.

“AI is moving very quickly, and there are many factors, of which energy efficiency is just one,” says Jeff Hutchins, OIF’s vice chair of the Energy Efficient Interfaces efforts, and of Ranovus, and one of the reports’ authors.

Despite the hyperscalers’ need to move quickly, they also recognise the value of standardisation. The OIF has published the reports to highlight key issues and help implement standards.

The Compute Optics Interface White Paper details the trade-offs in optical-scale-up interconnect but does not declare a winning approach.

What surprised the authors

The documents took a year to create. Did the work lead to any surprising insights?

Hutchins highlights bi-directional optics, saying he had not fully appreciated its benefits in terms of cost savings and reduced fibre count.

Also, the importance of latency: not just raw one-way latency, but what happens when communication goes wrong, such as retransmissions and error handling. Here, turnaround time is crucial in tightly synchronised AI accelerator systems.

One debate to be resolved is the choice between slow-and-wide links and fast serial ones for scale-up. What should be asked here is what can be built in volume, reliably, and in time, says Hutchins.

The OIF hopes the documents will lead to smaller-group convergence and even a multi-source agreement (MSA), followed by a more formal standards activity once the most practical path becomes clearer.

CMIS security additions

The OIF also recently approved security additions to the Common Management Interface Specification (CMIS).

The goal is to add trust to the links that CMIS uses to set up pluggable modules for authentication, authorisation, and resistance to interception as part of the CMIS commands.

AI is forcing both pragmatism and engineering excellence

Tracy says this period, driven by AI’s scaling needs, is remarkable but not unique. There have been other times when market dynamics have driven developments that meet the needs yet may not use the most elegant engineering solutions.

“We could talk for months about the most optimal way to do things, but there is some brute force going on where that is good enough,” says Tracy. “That said, there is some very exquisite engineering going on to solve some really hard problems that this market faces.”

Tracy cites as an example the CEI-448G work: “It will absolutely be exquisite by the time we’re all done with it.”

The new signalling rate is going to bring with it challenges that, for Tracy, represent an intersection of several factors.

AI cluster sizes are getting bigger, requiring longer reach, yet signalling rates are doubling and higher bandwidth densities are required.

All this raises challenges: rising energy consumption, thermal management issues, and delivering greater functionality over management buses.

“It is the intersection of all the things that the OIF does,” concludes Tracy. “And when we bring all of those challenges together, that is where very careful engineering must occur.”