OIF adds a short-reach design to its 1600ZR/ ZR+ portfolio

The OIF (Optical Internetworking Forum) has broadened its 1600-gigabit coherent optics specification work to include a third project, complementing the 1600ZR and 1600ZR+ initiatives.

The latest project will add a short-reach ‘coherent-lite’ digital design to deliver a reach of 2km to 20km and possibly 40km with a low latency below 300ns

The low latency will suit workloads and computing resources distributed across data centres.

“The coherent-lite is more than just the LR (long reach) work that we have done [at 400 gigabits and 800 gigabits],” says Karl Gass, optical vice chair of the OIF’s physical link layer (PLL) working group, adding that the 1600-gigabit coherent-lite will be a distinct digital design.

Doubling the data rate from 800 gigabits to 1600 gigabits is the latest battle line between direct-detect and coherent pluggable optics for reaches of 2km to 40km.

At 800 gigabits, the OIF members debated whether the same coherent digital signal processor would implement 800ZR and 800-gigabit LR. Certain OIF members argued that unless a distinct, coherent DSP is developed, a coherent optics design will never be able to compete with direct-detect LR optics.

“We have that same acknowledgement that unless it’s a specific design for [1600 gigabit] coherent-lite, then it’s not going to compete with the direct detect,” says Gass.

OIF’s 1600-gigabit specification work

The OIF’s 1600-gigabit roadmap has evolved rapidly in the last year.

In September 2023, the OIF announced the 1600ZR project to develop 1.6-terabit coherent optics with a reach of 80km to 120km. In January 2024, the OIF announced it would undertake a 1600ZR+ specification, an enhanced version of 1600ZR with a reach of 1,000km.

The OIF’s taking the lead in ZR+ specification work is a significant shift in the industry, promising industry-wide interoperability compared to the previous 400ZR+ and 800ZR+ developments.

Now, the OIF has started a third 1600-gigabit coherent-lite design.

1600ZR development status

Work remains to complete the 1600ZR Implementation Agreement, the OIF’s specification document. However, member companies have agreed upon the main elements, such as the framing schemes for the client side and the digital signal processing and using oFEC as the forward error correction scheme.

oFEC is a robust forward error correction scheme but adds to the link’s latency. It has also been chosen as the forward error correction scheme for 1600ZR. The OIF members want the ‘coherent-lite’ version to use a less powerful forward error correction to achieve lower latency.

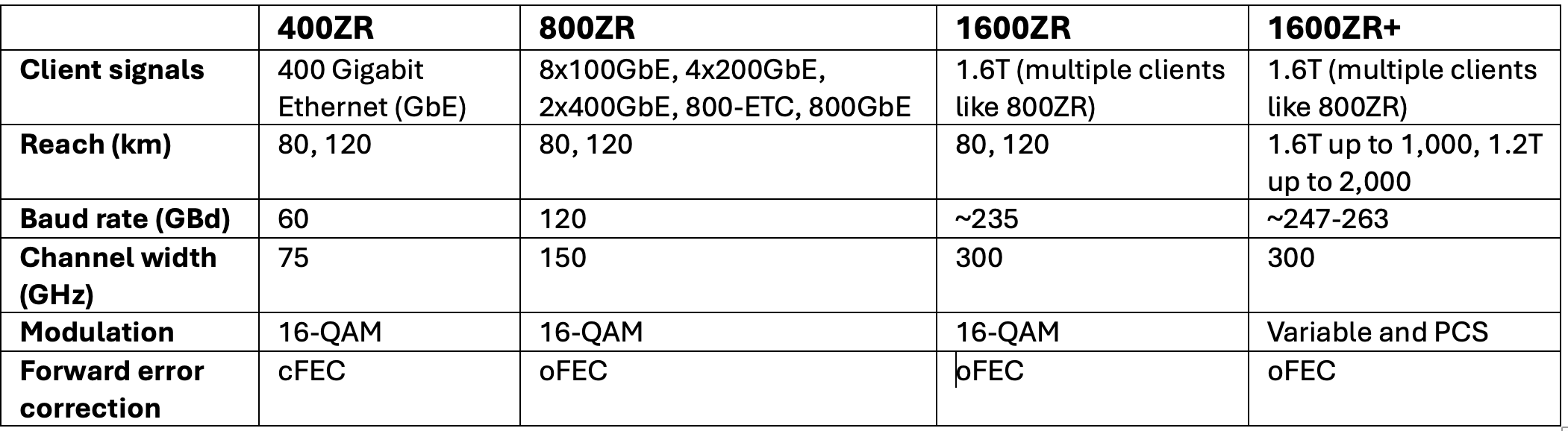

The 1600ZR symbol rate chosen is around 235 gigabaud (GBd), while the modulation scheme is 16-ary quadrature amplitude modulation (16-QAM). The specified reach will be 80km to 120km. (See table below.)

The members will likely agree on the digital issues this quarter before starting the optical specification work. Before completing the Implementation Agreement, members must also spell out interoperability testing.

1600ZR+ development status

The 1600ZR+ work still has some open questions.

One is whether members choose a single carrier, two sub-carriers, or four to achieve the 1,000km reach. The issue is equalisation-enhanced phase noise (EEPN), which imposes tighter constraints on the received laser. Using sub-carriers, the laser constraints can be relaxed, enabling more suppliers. The single-carrier camp argues that sub-carriers complicate the design of the coherent digital signal processor (DSP).

The workgroup members have also to choose the probabilistic constellation shaping to use. Probabilistic constellation shaping gain can extend the reach, but it can also reduce the symbol rate and, hence, the bandwidth specification of the coherent modem’s components.

The symbol rate of the 1600ZR+ is targeted in the range of 247GBd to 263GBd.

Power consumption

The 1600ZR design’s power consumption was hoped to be 26W, but it is now expected to be 30W or more. The 1600ZR+ is expected to be even higher.

The coherent pluggable’s power consumption will depend on the CMOS process that the coherent DSP developers choose for their 1600ZR and 1600ZR+ ASIC designs. Will they choose the state-of-the-art 3nm CMOS process or wait for 2nm or even 1.8nm to become available to gain a design advantage?

Timescales

The target remains to complete the 1600ZR Implementation Agreement document quickly. Gass says the 1600ZR and 1600ZR+ Implementation Agreements could be completed this year, paving the way for the first 1600ZR/ZR+ products in 2026.

“We are being pushed by customers, which isn’t a bad thing,” says Gass.

The coherent-lite design will be completed later given that it has only just started. At present, the OIF will specify the digital design and not the associated optics, but this may change, says Gass.

Ciena sends a 1.6T optical lambda over a 470km link

- Ciena has detailed the first live field trial using its WaveLogic 6 Extreme coherent modem.

- The WaveLogic 6 modem will be generally available from the end of the month.

Ciena’s newest coherent optical modem has sent 1.6 terabits of data over a 470km link. The field trial used Ciena’s WaveLogic 6 Extreme coherent modem in telecom operator Arelion’s live network.

The link connects an Equinix data centre in Ashburn to a Telxius submarine cable landing station, both sites in the state of Virginia.

“The fact that we are achieving 1.6-terabit wavelengths across close to 500 kilometres is a testament to the performance and integrity of the design,” says Helen Xenos, senior director of portfolio marketing at Ciena.

Ciena has won over 20 orders for the WaveLogic 6 Extreme from telecom operators and hyperscalers.

In Ciena’s latest quarterly results, CEO Gary Smith mentioned how Ciena had won business with significant cloud providers covering terrestrial, submarine, and coherent pluggable applications. “The majority [of these are] driven by expected growth in AI and cloud traffic,” said Smith.

WaveLogic 6 Extreme DSP

Ciena announced its WaveLogic 6 Extreme digital signal processor (DSP) early in 2023.

The WaveLogic 6 Extreme is the industry’s first 3nm CMOS process coherent DSP with a maximum symbol rate of 200 gigabaud (GBd). Current leading coherent DSPs deployed use symbol rates ranging from 120-150GBd and support up to 1.2-terabit wavelengths.

The Ciena DSP can execute 1,600 trillion (1.6 x 1015) operations per second and uses the equivalent of 4km of on-chip copper interconnect.

In contrast, Ciena’s leading deployed DSP device—the WaveLogic 5 Extreme, announced in 2019—is a 7nm CMOS DSP. Over 300 customers have ordered the WaveLogic 5 Extreme.

When it was first announced, the WaveLogic 5 had a baud rate ranging from 60 to 95GBd. Now, its baud rate ranges from 71.0 to 106.9GBd. This highlights how the coherent modem performance has been improved over the years and the same should be expected for the WaveLogic 6 Extreme.

Arelion trial

The Arelion trial is the first Ciena has announced.

“It’s a high bandwidth route connecting a submarine landing station to the data centre capital of the world – Ashburn, Virginia,” says Xenos. “It’s an ideal link to show how WaveLogic 6 can support this massive data volume transmission at today’s fastest speeds.”

The optical wavelength sent 1.6 terabits per second (Tbps) of data over nearly 500 km reach. The WaveLogic 5 Extreme, when first announced, sent 800Gbps some 200km.

“The performance that we can achieve at the highest line rate with WaveLogic 6 is better than what we were able to achieve at the highest line rate with WaveLogic 5 Extreme,” says Xenos. This is because a 3nm CMOS process can cram more digital logic on-chip, enabling the execution of advanced digital signal processing algorithms.

The WaveLogic 6 Extreme improves spectral efficiency by 15 per cent over existing links. The device also delivers 0.25-1 decibel (dB) of signal performance improvement by better tackling nonlinearities introduced by the communication channel during transmission.

The DSP also uses multi-dimensional coding technology to tackle noisy and nonlinear impaired fibre links.

Ciena expects to be able to send 1.6-terabit wavelengths several hundred kilometres over metro networks that feature reconfigurable optical add-drop multiplexers (ROADMs).

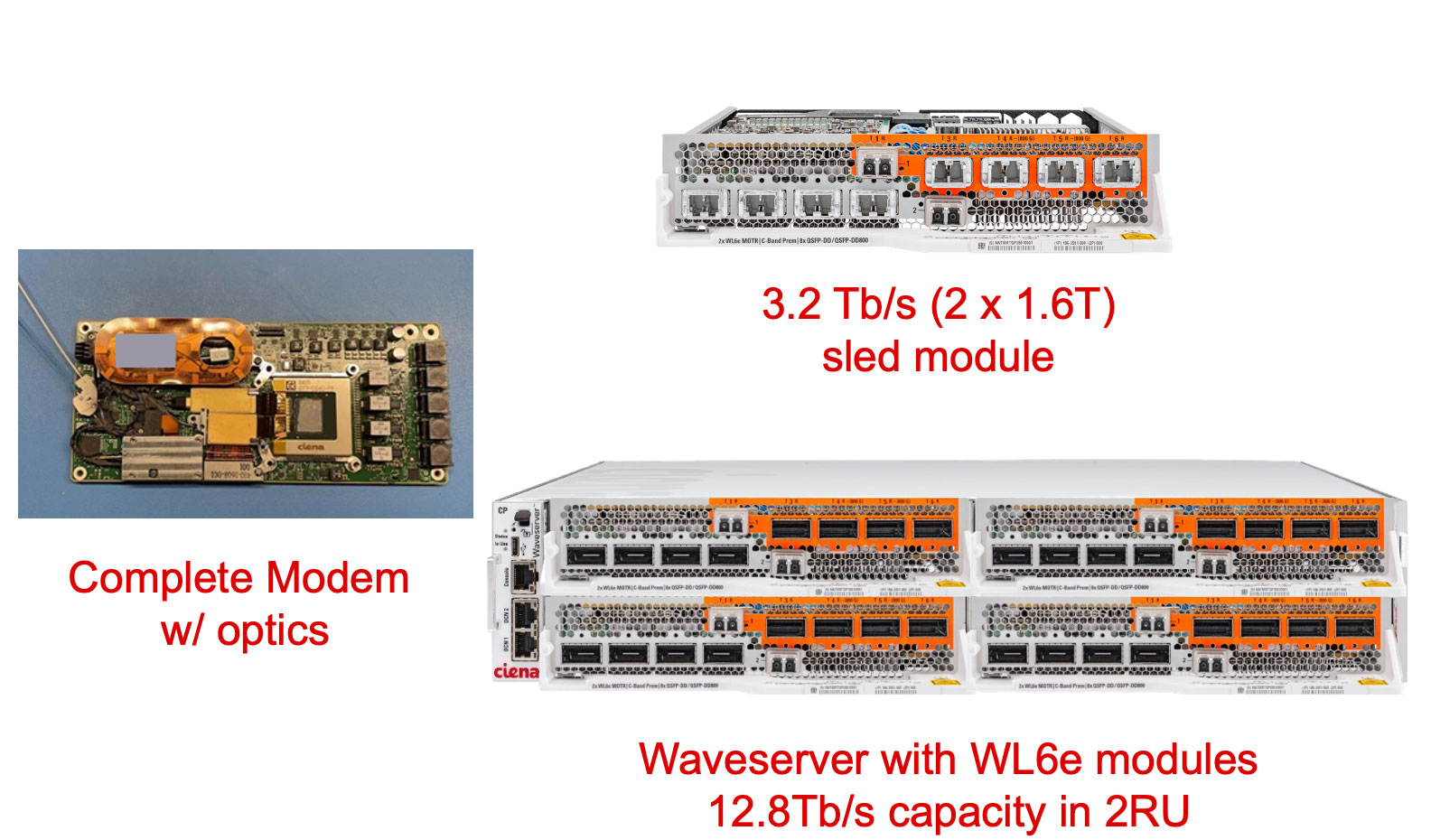

The Arelion trial used Ciena’s Waveserver, a two-rack-unit (2RU) optical transport chassis and Ciena’s open 6500 reconfigurable line system (see image below).

The Waveserver chassis uses insertable sleds, each sled hosting two WaveLogic 6 Extreme coherent modems. Four sleds fit into the Waveserver chassis for a total of eight optical wavelengths and 12.8Tbps transmission capacity.

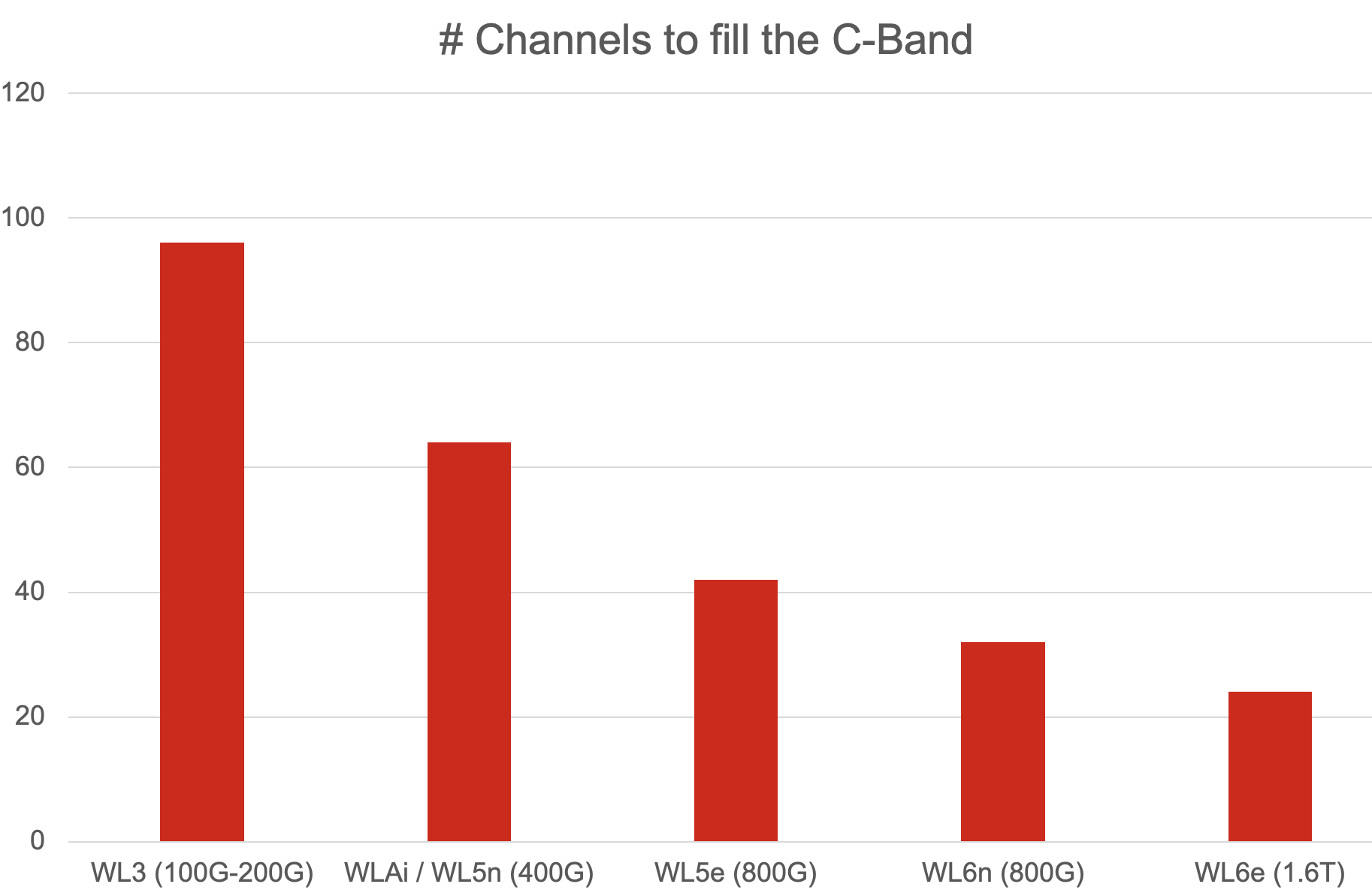

Overall, 24 1.6Tbps wavelengths, each occupying a 200GHz channel, fit into a fibre’s C-band spectrum, giving a total capacity of 38.4Tbps. The same applies to the fibre’s L-band.

“You are filling up the full C-band with only 24 wavelengths,” says Xenos. “It wasn’t that long ago when we filled the C-band with 96, 100-gigabit channels or 64, 400-gigabit channels.” (See chart.)

Ciena says other field trials are planned. Based on its simulation work, Ciena expects its latest coherent modem to send 1.2Tbps across the Atlantic Ocean, 1Tbps across the Pacific Ocean, and 800Gbps over 3,000km. “We expect to see performance improvements because we are still tweaking,” says Xenos.

Embedded and pluggable modules

Coherent pluggable optics continue to advance, especially with the demands of hyperscalers. Coherent pluggable modules, driven by hyperscalers’ data centre interconnect demands, also continue to advance. So, is the requirement for the highest-performance embedded modules diminishing?

Ciena believes that both classes of devices are needed: performance-optimised (embedded) and pluggable coherent optical modules.

“There are more capabilities that are becoming available in pluggables, with the 800-gigabit generation extending to 1,000km and beyond and with L-band offerings coming in the near future,” she says. “If you can integrate the pluggable into a router platform, that allows you to save on space and power.”

However, the pluggable can’t match the spectral efficiency of an embedded coherent module. An 800-gigabit pluggable uses a 150GHz channel spacing, which is the same spectral efficiency as the earlier generation Ciena WaveLogic AI.

The latest embedded modules, in contrast, can be significantly better than equivalent line reate pluggables: from 1.3x to 2x. This is an important consideration in environments where fibre is scarce.

Another point Xenos makes is the nature of the optical network and its total cost, not just the optics (embedded or pluggable) but also the optical line system. If a link has many amplification stages and ROADMs, the optical line makes a more significant contribution to the overall cost. Here embedded optics is needed to span the more complex optical route while being one part of the overall cost.

“You have to look at the total overall cost of building the network,” says Xenos. “It is the optics and the photonic line system.”

General availability

The WaveLogic 6 Extreme will be generally available at the end of September 2024.

When Ciena first announced the coherent DSP, the company expected the device to be generally available in the first half of 2024. In March at OFC 2024, Ciena gave an update saying trials would start this summer.

Xenos says the delivery date did slip by several months. But she stresses the achievement of delivering such a complex coherent modem system. As well as designing the chip in a 3nm CMOS process, the DSP also includes very high-speed mixed-signal analogue-to-digital and digital-to-analogue converters.

“When you target a certain availability, it is the best date that is also realistic,” says Xenos. “The fact that we’re only a few months off means that the team has executed to deliver a working product.”

Ciena is also integrating WaveLogic 6 into its 6500 optical transport platform and will make a coherent WaveLogic 6 module available for OEMs or developers that have custom equipment requirements.

Meanwhile, Ciena continues to develop the Nano, the second WaveLogic 6 device designed for the coherent pluggable market. The WaveLogic 6 Nano is expected to be sampled at the end of the year.

Market consolidation

In June, Nokia announced its intention to acquire Infinera. If the deal passes regulatory approval, it will reduce the number of companies capable of developing high-end coherent DSPs.

More players mean greater competition which pushes the marketplace. But developing coherent DSPs using shrinking CMOS nodes is getting more expensive. One fewer player can be viewed as good news for the rest. Xenos says Ciena has expected fewer high-end coherent players going forward.

“Those who are vertically integrated have an advantage of improved cost efficiencies that they can offer to their end-customers,” she says. “And we’ve been investing in vertical integration because it allows us to control our destiny and come to market with new technology at an earlier time.”

This is what the company has done with the WaveLogic 6 Extreme, where Ciena had to develop its own 100GHz analogue bandwidth coherent optics to achieve the 200GBd symbol rate.

Future developments

The roadmap for coherent pluggable modules is well defined due to the industry organisation, the OIF’s 1600ZR and 1600ZR+ 1.6Tbps coherent pluggable modules which are expected from 2028. For embedded modules the roadmap is less clear.

“There is nothing to announce at this time, but we know that the next step has to be bold enough to provide a meaningful benefit for its adoption into the network,” says Xenos.