From spin-out to scale-up: OpenLight’s $34M funding

Part 1: Start-up funding

OpenLight Photonics, a Santa Barbara-based start-up specialising in silicon photonics, has raised $34 million in an oversubscribed Series A funding round.

The start-up will use the funding to expand production and its photonic integrated circuit (PIC) design staff.

OpenLight Photonics raises $34M in an oversubscribed Series A.

“We’re starting to get customers taking in production mask sets, so it’s about scaling operations and how we handle production,” says OpenLight CEO, Adam Carter (pictured). The start-up needs more PIC designers to work with customers.

Technology

OpenLight’s technology originated at Aurrion, a fabless silicon photonics start-up from the University of California, Santa Barbara.

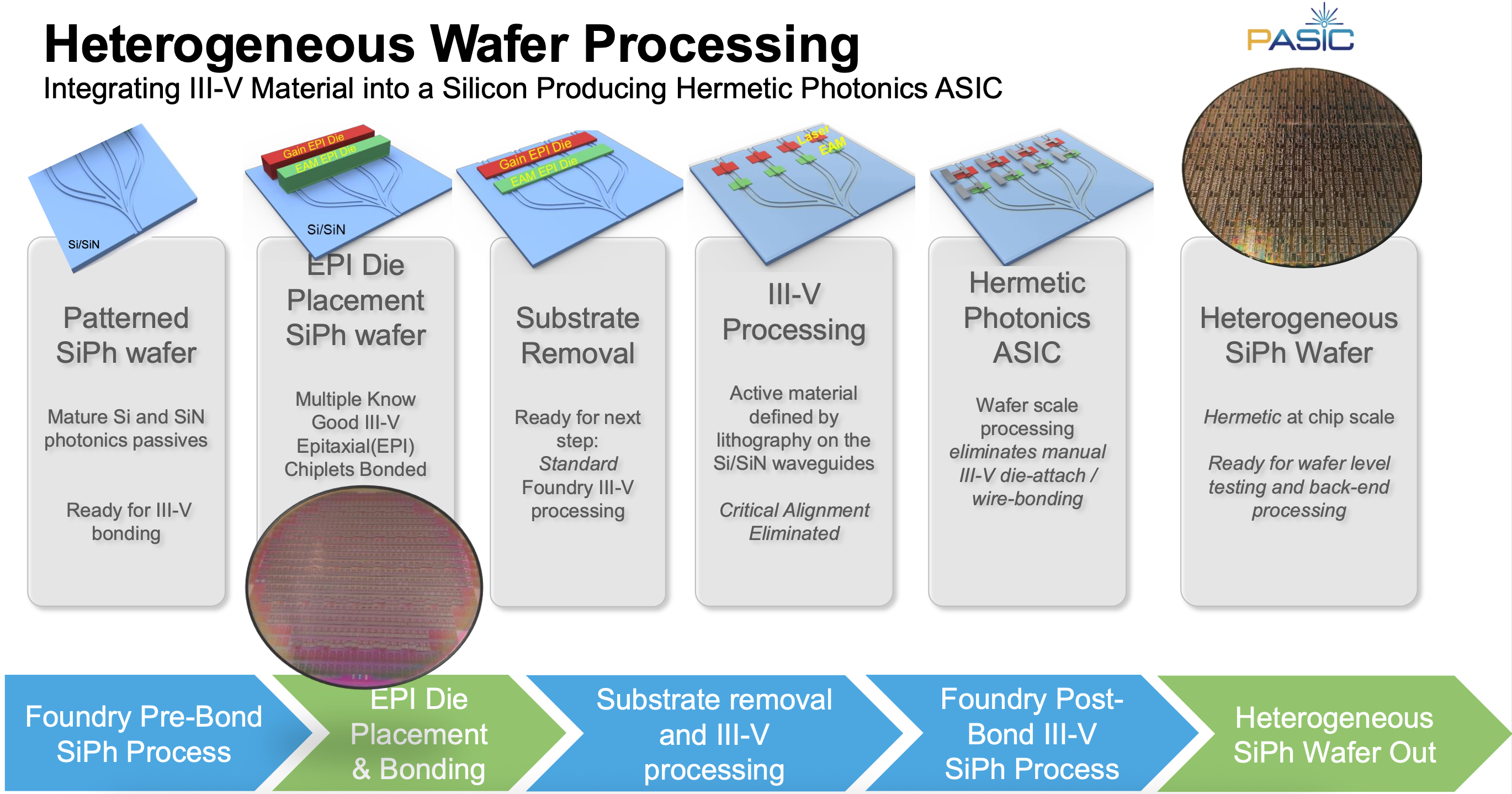

Aurrion’s heterogeneous integration silicon photonics technology supports III-V materials, enabling components such as lasers, modulators, and optical amplification to be part of a photonic integrated circuit (PIC). Intel has its own heterogeneous integration silicon photonics process, which it has used to make millions of pluggable optical transceivers. OpenLight is offering the technology to customers effectively as a photonic ASIC design house.

Juniper Networks bought Aurrion in 2016 and, in 2022, spun out the unit that became OpenLight. Electronic design tool specialist Synopsys joined Juniper in backing the venture. Synopsys announced it was acquiring simulation company Ansys, a $35 billion deal it completed in July. Given that Synopsys would be focused on integrating Ansys, it suggested to OpenLight in January that they should part ways.

Funding

“We were only looking for $25 million to start with, and we finished at $34 million,” says Carter. Capricorn Investment Group was a late entrant and wanted to co-lead the funding round. Given initial commitments from other funders, Mayfield and Xora Innovation, set specific ownership percentages, it required an increase to accommodate Capricorn.

Xora’s first contact with OpenLight was after it approached the start-up’s stand at the OFC 2025 event held in March.

Juniper—now under HPE—is also an investor. The company played a key role in helping OpenLight while it sought funding. “Juniper could see that we were very close to an intercept point regarding our business model and our customers, so that’s why Juniper invested,” says Carter.

HPE continually looks at technologies it will require; silicon photonics with heterogeneous integration is one such technology, says Carter. However, HPE has no deal with OpenLight at this time.

Design roadmap

OpenLight is developing a 1.6-terabit PIC, now at an advanced prototype (beta) stage. The design uses eight channels for a 1.6T-DR8 OSFP pluggable design, implemented using four lasers and eight modulators, each operating at 200 gigabit-per-second (Gbps).

Carter says the first wafers will come from foundry Tower Semiconductor around October. This will be OpenLight’s largest production run — 100 wafers in four batches of 25. Some ten customers will evaluate the PICs, potentially leading to qualification.

A coarse wavelength division multiplexing (CWDM) 1.6-terabit design will follow in 2026. The CWDM uses 4 wavelengths, each at 200Gbps, on a fibre, with two such paths used for the 1.6T OSFP-XD 2xFR4 optical module.

The company is also pushing to develop 400Gbps channels, increasing the frequency response and improving the extinction ratio through process changes.

“We’ve got a whole series of experiments coming out over the next few months,“ says Carter. The frequency response of the indium phosphide modulator has already been improved by 10 gigahertz (GHz) to 90-95GHz. The process changes will be adopted for some alpha sample wafers in production that may enable modulation at 400Gbps, hence a 3.2-terabit PIC design.

“If we can show some good 3.2-terabit eyes, just as a demo, it shows that there’s a technology route to get there whenever 3.2-terabit modules are needed,” he says.

Customer growth

OpenLight’s customers have grown from three in 2023 to 17 last year to 20 actively designing. “We are growing the pipeline,” says Carter.

Early adopters were start-ups, but now larger firms are engaging Openlight. “Investors noted start-ups take more risk, but now bigger companies are coming in to drive volume,” says Carter.

Optical interconnect will drive initial volumes, but automotive and industrial sensing will follow. “The mix will change, but for the next couple of years, the revenues will be from optical interconnect,” says Carter.

Co-packaged optics is another interconnect opportunity. Here, OpenLight’s integrated laser technology would not be needed, given the co-packaged optics designs favour external laser sources. Instead, the company can offer integrated indium phosphide modulator banks or modulator banks with semiconductor optical amplifiers (SOAs), their compact size—“microns, not millimetres”—aiding packaging.

In addition to the foundry Tower Semiconductor for its wafers, OpenLight partners with Jabil, Sanmina, and TFC for the packaging and does its testing via ISC, an ASE subsidiary.

“They know test and certain customers with ISC, and ASE could do a complete turnkey solution,” says Carter. “But our priority is to get the test area set up to deal with the production; we’ve not had 100 wafers in a year being delivered for test.”

Silicon photonics

Carter, who was at Cisco when it acquired Lightwire in 2012, says silicon photonics’ potential to shrink optical designs was already recognised then. Since then, a lot of progress has been made, but now the focus is on building the supporting ecosystem. This includes a choice of foundries offering optical process design kits (PDKs) and outsourced assembly and test houses (OSATs) that can handle volumes.

Until now, silicon photonics has been all passive circuits. Now OpenLight, working with Tower and its PDK, is offering customers the ability to design and make heterogeneous integrated silicon photonics circuits. “Every customer gets the same PDK,” says Carter.

And it need not just be indium phosphide. The idea is to expand the PDK to support modulation materials such as polymer and thin-film lithium niobate. “If it is a better material, we’ll integrate it,” he says.

Having secured the funding, Carter is clear about the company’s priority: “It’s all about execution now.”

John Bowers: We are still at the dawn of photonics

After 38 years at the University of California, Santa Barbara (UCSB), Professor John Bowers (pictured) is stepping away from teaching and administrative roles to focus on research.

He welcomes the time it will free for biking and golf. He will also be able to linger, not rush, when travelling. On a recent trip to Saudi Arabia, what would have centered around a day-event became a week-long visit.

Bowers’ career includes significant contributions to laser integration and silicon photonics, mentoring some 85 PhD students, and helping found six start-ups, two of which he was the CEO.

Early Influences

Bowers’ interest in science took root while at high school. He built oscilloscopes and power supplies using Heathkits, then popular educational assemblies for electronics enthusiasts. He was also inspired by his physics and chemistry teachers, subjects he majored in at the University of Minnesota.

A challenging experience led him to focus solely on physics: “I took organic chemistry and hated it,” says Bowers. “I went, ‘Okay, let’s stick to inorganic materials.’”

Bowers became drawn to high-energy physics and worked in a group conducting experiments at Fermilab and Argonne National Laboratories. Late-night shifts – 10 PM to 6 AM – offered hands-on learning, but a turning point came when his mentor was denied tenure. “My white knight fell off his horse,” he says.

He switched to applied physics at Stanford, where he explored gallium arsenide and silicon acoustic devices, working under the supervision of the late Gordon Kino, a leading figure in applied physics and electrical engineering.

Bowers then switched to fibre optics, working in a group that was an early leader in single-mode optical fibre. “It was a period when fibre optics was just taking off,” says Bowers. “In 1978, they did the first 50-megabit transmission system, and OFC [the premier optical fibre conference] was just starting.”

Bell Labs and fibre optics

After gaining his doctorate, Bowers joined Bell Labs, where his work focused on the devices—high-speed lasers and photodetectors—used for fibre transmission. He was part of a team that scaled fibre-optic systems from 2 to 16 gigabits per second. However, the 1984 AT&T breakup signalled funding challenges, with Bell Labs losing two-thirds of its financial support.

Seeking a more stable environment, Bowers joined UCSB in 1987. He was attracted by its expertise in semiconductors and lasers, including the presence of the late Herbert Kroemer, who went on to win the 2000 Nobel Prize in Physics. Kroemer developed the double heterostructure laser and played a big part in enticing Bowers to join. Bowers was tasked with continuing the laser work, something he has done for the last 40 years.

“Coming to Santa Barbara was brilliant, in retrospect,” says Bowers, citing its strong collaborative culture and a then newly formed materials department.

Integrated lasers

At UCSB, Bowers worked on integrated circuits using indium phosphide, including tunable lasers and 3D stacking of photonic devices.

At the same time, the field of silicon photonics was starting after Richard Soref wrote a seminal paper proposing silicon as an optical material for photonic integrated circuits (PIC).

“We all knew that silicon was a terrible light emitter because it is an indirect band-gap material,” says Bowers. “So when people started talking about silicon photonics, I kept thinking: ‘Well, that is fine, but you need a light source, and if you don’t have a light source, it’ll never become important.’”

Bowers tackled integrating lasers onto silicon to address the critical need for an on-chip light source. He partnered with Intel’s Mario Paniccia and his team, which had made tremendous progress developing a silicon Raman lasers with higher powers and narrower linewidths.

“It was very exciting, but you still needed a pump laser; a Raman laser is just a wavelength converter from one wavelength to another,” says Bowers. “So I focused on the pump laser end, and the collaboration benefitted us both.”

Intel commercialised the resulting integrated laser design and sold millions of silicon-photonics-based pluggable transceivers.

“Our original vision was verified: the idea that if you have CMOS processing, the yields will be better, the performance will be better, the cost will be lower, and it scales a lot better,” says Bowers. “All that has proven to be true.

Is Bowers surprised that integrated laser designs are not more widespread?

All the big silicon photonics companies, including foundry TSMC, will incorporate lasers into their products, he says, just as Intel has done and Infinera before that.

Infinera, an indium phosphide photonic integrated circuit (PIC) company now acquired by Nokia, claimed that integration would improve the reliability and lower the cost, says Bowers: “Infinera did prove that with indium phosphide and Intel did the same thing for silicon.”

The indium phosphide transceiver has a typical failure rate of 10 FIT (failures per ten billion hours), and if there are 10 laser devices, the FIT rises to 100, he says. By contrast, Intel’s design has a FIT of 0.1, and so with 10, the FIT becomes on the order of 1.

Silicon lasers are more reliable because there’s no III-V material exposed anywhere. Silicon or silicon dioxide facets eliminate the standard degradation mechanisms in III-V materials. This enables non-hermetic packaging, reducing costs and enabling rapid scaling.

According to Bowers, Intel scaled to a million transceivers in one year. Such rapid scaling to high volumes is important for many applications, and that is where silicon photonics has an advantage.

“Different things motivate different people. For me, it’s not about money, it’s more about your impact, particularly on students and research fields. To the extent that I’ve contributed to silicon photonics becoming important and dynamic, that is something I’m proud of.”

-Professor John Bowers

Optical device trends

Bowers notes how the rise of AI has surprised everyone, not just in terms of the number of accelerator chips needed but their input-output (I/O) requirements.

Copper has been the main transmission medium since the beginning of semiconductor chips, but that is now being displaced by optics – silicon photonics in particular – for the communications needs of very high bandwidth chips. He also cites companies like Broadcom and Nvidia shipping co-packaged optics (CPO) for their switching chips and platforms.

“Optics is the only economic way to proceed, you have to work on 3D stacking of chips coupled with modern packaging techniques,” he says, adding that the need for high yield and high reliability has been driving the work on III-V lasers on silicon.

One current research focus for Bowers is quantum dot lasers, which reduce the line width and minimise reflection sensitivity by 40dB. This eliminates the need for costly isolators in datacom transceivers.

Quantum dot devices also show exceptional durability, with lifetimes for epitaxial lasers on silicon a million times longer than quantum well devices on silicon and 10 times less sensitivity to radiation damage, as shown in a recent Sandia National Labs study for space applications.

Another area of interest is modulators for silicon photonics. Bowers says his group is working on sending data at 400 gigabits-per-wavelength using ‘slow light’ modulators. These optical devices modulate the intensity or phase, of light. Slowing down the light improves its interaction in the material, improving efficiency and reducing device size and capacitance. He sees such modulators is an important innovation.

“Those innovations will keep happening; we’re not limited in terms of speed by the modulator,” says Bowers, who also notes the progress in thin-film lithium niobate modulators, which he sees as benefiting silicon photonics, “We have written papers suggesting most of the devices may be III-V,” says Bowers, and the same applies to materials such as thin-film lithium niobate.

“I believe that as photonic systems become more complex, with more lasers and amplifiers, then everyone will be forced to integrate,” says Bowers.

Other applications

Beyond datacom, Bowers sees silicon photonics enabling LIDAR, medical sensors, and optical clocks. His work on low-noise lasers, coupled to silicon nitride waveguides, reduces phase noise by 60dB, enhancing sensor sensitivity. “If you can reduce the frequency noise by 60dB, then that makes it either 60dB more efficient, or you need 60dB less power,” he says.

Applications include frequency-based sensors for gas detection, rotation sensing, and navigation, where resonance frequency shifts detect environmental changes.

Other emerging applications include optical clocks for precise timing in navigation, replacing quartz oscillators. “You can now make very quiet clocks, and at some point we can integrate all the elements,” Bowers says, envisioning chip-scale solutions.

Mentorship and entrepreneurial contributions

Bowers’ impact extends to mentorship, guiding so many PhD students who have gone on to achieve great success.

“It’s very gratifying to see that progression from an incoming student who doesn’t know what an oscilloscope is to someone who’s running a group of 500 people,” he says.

Alan Liu, former student and now CEO of the quantum dot photonics start-up Quintessent, talks about how Bowers calls on his students to ‘change the world’.

Liu says it is not just about pushing the frontiers of science but also about having a tangible impact on society through technology and entrepreneurship.”

Bowers co-founded UCSB’s Technology Management Department and taught entrepreneurship for 30 years. Drawing on mentors like Milton Chang, he focused on common start-up pitfalls: “Most companies fail for the same set of reasons.”

His own CEO start-up experience informed his teaching, highlighting interdisciplinary skills and team dynamics.

Mario Paniccia, CEO of Anello Photonics, who collaborated with Bowers as part of the Intel integrated laser work, highlights Bowers’ entrepreneurial skills.

“John is one of the few professors who are not only brilliant and technically a world expert – in John’s case, in III-V materials – but also business savvy and entrepreneurial,” says Paniccia. “He is not afraid to take risks and can pick and hire the best.”

Photonics’ future roadmap

Bowers compares photonics’ trajectory to electronics in the 1970s, when competing CMOS technologies standardised, shifting designers’ focus from device development to complex circuits. “Just like in the 1970s, there were 10 competing transistor technologies; the same consolidation will happen in photonics,” he says.

Standardised photonic components will be integrated into process design kits (PDKs), redirecting research toward systems like sensors and optical clocks.

“We’re not at the end, we’re at the beginning of photonics,” emphasises Bowers.

Reflections

Looking back, would he have done anything differently?

A prolonged pause follows: “I’ve been very happy with the choices I have made,” says Bowers, grateful for his time at UCSB and his role in advancing silicon photonics.

Meanwhile, Bowers’ appetite for photonics remains unwavering: “The need for photonic communication, getting down to the chip level, is just going to keep exploding,” he says.

OFC 2025 industry reflections - Final Part

Gazettabyte has been asking industry figures for their thoughts after attending the OFC conference held in San Francisco.

In the final part, Arista’s Vijay Vusirikala and Andy Bechtolsheim, Chris Doerr of Aloe Semiconductor, Adtran’s Jörg-Peter Elbers, and Omdia’s Daryl Inniss share their learnings. Vusirikala, Doerr, and Elbers all participated in OFC’s excellent Rump Session.

Vijay Vusirikala, Distinguished Lead, AI Systems and Networks, and Andy Bechtolsheim, Chief Architect, at Arista Networks.

OFC 2025 wasn’t just another conference. The event felt like a significant momentum-gaining inflexion point, buzzing with an energy reminiscent of the Dot.com era optical boom.

This palpable excitement, reflected in record attendance and exhibitor numbers, was accentuated for the broader community by the context set at Nvidia’s GTC event held two weeks before OFC, highlighting the critical role optical technologies play in enabling next-generation AI infrastructure.

This year’s OFC moved beyond incremental updates, showcasing a convergence of foundational technologies and establishing optics not just as a supporting player but a core driver in the AI era. The scale of innovation directed towards AI-centric solutions – tackling power consumption, bandwidth density, and latency – was striking.

Key trends that stood out were as follows:

Lower Power Interconnect technologies

The overarching topic was the need for more power-efficient optics for high-bandwidth AI fabrics. Legacy data centre optics are impacting the number of GPUs that fit into a given data centre’s power envelope.

Three main strategies were presented to address the power issue.

First, whenever possible, use copper cables, which are far more reliable and cost less than optics. The limitation, of course, is copper’s reach, which at 200 gigabit-per-lane is about 1-2m for passive copper cables and 3-4m for active redriven copper cables.

Second, eliminate the traditional digital signal processor (DSP) and use linear interface optics, including Linear Pluggable Optics (LPO), Near Package Optics (NPO), and Co-Packaged Optics (CPO), all of which offer substantial (60%) power savings, lower latency, and higher reliability compared to traditional DSP solutions.

The biggest difference between linear pluggable optics and co-packaged optics is that linear pluggable optics retains the well-known operational advantages of pluggable modules: configurability, multi-vendor support, and easy field serviceability (hot-swapping at module level), compared to fixed optics like co-packaged optics, which require chassis-level RMAs (return materials authorisation). It remains to be seen whether co-packaged optics can overcome the serviceability issues.

Third, developments in a host of new technologies – advances in copper interconnects, microLED-based interconnects, and THz-RF-over-waveguides – promise even lower power consumption than current silicon photonics-based interconnect technologies.

We look forward to hearing more about these new technologies next year.

Transition from 200 gigabit-per-lambda to 400 gigabit-per-lambda

With the 200 gigabit-per-lambda optical generation just moving into volume production in 2025-26, attention has already turned to the advancement and challenges of 400 gigabit-per-lambda optical technologies for future high-speed data transmission, aiming towards 3,200 gigabit (8×400 gigabit) modules.

Several technical approaches for achieving 400 gigabit-per-lambda were discussed, including PAM-4 intensity modulation direct detection (IMDD), PAM-4 dual-polarisation, and optical time division multiplexing (OTDM). The technology choices here include indium phosphide, thin-film lithium niobate (TFLN), and silicon photonics, which are compared based on RF (radio frequency) loss, integration, cost, and high-volume readiness.

For 400 gigabit lambda optics, indium phosphide and thin-film lithium niobate are strong candidates, as silicon photonics will struggle with the high bandwidth.

At this point, it is impossible to predict which platform will emerge as the high-volume winner. Delivering power and cost-effective 400-gigabit lambda optics will require a concerted industry effort from optical component suppliers, connector suppliers, and test and measurement vendors.

Multi-core fibre

A new pain point in large AI data centres is the sheer number of fibre cables and their associated volume and weight. One way to solve this problem is to combine multiple fibre cores in a single fibre, starting initially with four cores, which would offer a 4:1 reduction in fibre count, bulk, and weight.

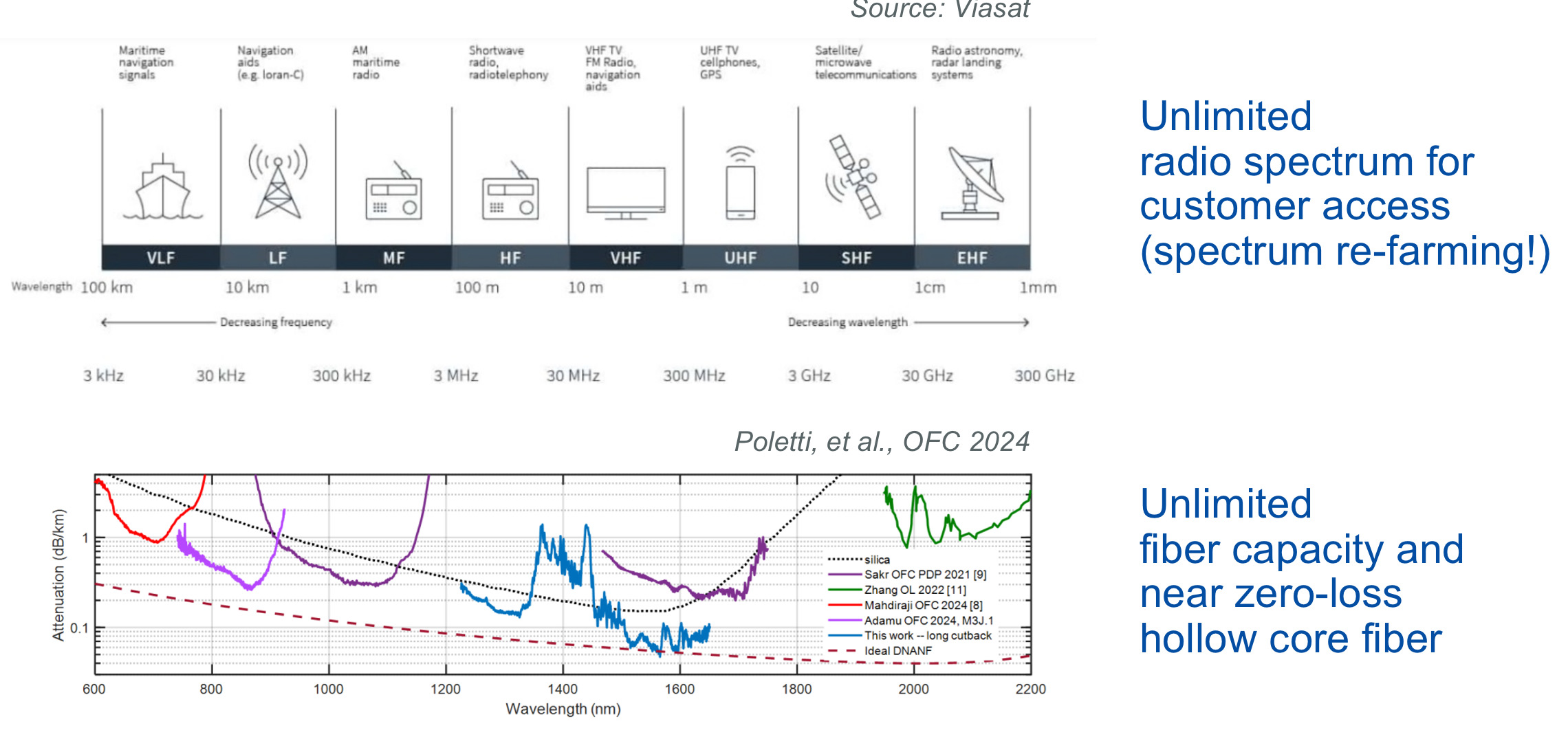

Hollow-core fibre

Innovation continues in the foundational fibre itself. Hollow-core fibre generated significant buzz, with its potential for lower latency and wider bandwidth attracting intense interest.

The maturing hollow-core fibre ecosystem, including cabling and interconnection progress, suggests deployments beyond niche applications like high-frequency trading may be approaching, reaching areas like distributed AI processing.

AI-driven network evolution

AI isn’t just driving network demand, it is increasingly becoming a network management tool.

Numerous demonstrations showcased AI/machine learning applications for network automation, traffic prediction, anomaly detection, predictive maintenance – e.g., analysing optical time-domain reflectometer (OTDR) traces, configuration management, and resource optimisation. This represents a fundamental shift towards more efficient, reliable, self-configuring, self-healing, and self-optimising networks.

Along with the many technical talks and tutorials, show floor demos, and customer and supplier meetings, OFC attendees also had a chance to combine technology with some light-hearted fun at the rump session.

This year’s topic was rebuilding global communication infrastructure after an alien invasion, and three teams came up with thought-provoking ideas for this theme.

Chris Doerr, CEO of Aloe Semiconductor

The best way to describe OFC 2025 is a giant Mars dust storm that raged for days. The swirling sand made it difficult to see anything clearly, and the sound was so loud you couldn’t think.

Acronyms ending in “O” were hitting you from all sides: LPO, LRO, NPO, CPO, OIO. The wind blew away sand that had buried old technologies, such as lithium niobate, electro-optic polymer, and indium-phosphide modulators, and they joined the fray.

Only now that the storm has somewhat subsided can we start piecing together what the future holds.

The main driver of the storm was, of course, artificial intelligence (AI) systems. AI requires a vast number of communication interconnects. Most interconnects, at least within a rack, are still copper. While copper keeps making incredible strides in density and reach, a fibre-optic interconnect takeover seems more and more inevitable.

The Nvidia announcements of co-packaged optics (CPO), which go beyond co-packaged optics and deserve a new name, such as optical input-output (OIO) or system-on-chip (SOC), created a great deal of excitement and rethinking. Nvidia employs a silicon interposer that significantly increases the electrical escape density and shortens the electrical links. This is important for the long-term evolution of AI computing.

The CPO/OIO/SOC doesn’t mean the end of pluggables. Pluggables still bring tremendous value with attributes such as time-to-market, ecosystem, replaceability, etc.

Most pluggables will still be fully retimed, but 100 gigabit-per-lane seems comfortable with linear pluggable optics (LPO), and 200 gigabit-per-lane is starting to accept linear receive optics (LRO).

For 200 gigabit per lane, electro-absorption modulated lasers (EMLs) and silicon photonics have comfortably taken the lead. However, for 400 gigabit per lane, which had two main demos on the show floor by Ciena and Marvell, many technologies are jockeying for position, mostly EMLs, thin-film lithium niobate (TFLN), indium phosphide, and silicon photonics.

Many companies are abandoning silicon photonics, but this author feels this is premature. There were demos at OFC of silicon photonics attaining near 400 gigabit-per-lane, and the technology is capable of it.

An important thing to remember is that the new OIO/SOC technology is silicon photonics and comes from a CMOS foundry. Putting non-CMOS materials such as thin-film lithium niobate or indium phosphide in such a platform could take years of expensive development and is thus unlikely.

In summary, OFC 2025 was very active and exciting. Significant technology improvements and innovations are needed.

The dust is far from settled, so we must continue wading into the storm and trying to understand it all.

Jörg-Peter Elbers, Senior Vice President, Advanced Technology, Standards and IPR, Adtran

OFC 2025 marked its largest attendance since 2003 with nearly 17,000 visitors, as it celebrated its 50th anniversary.

Discussions in 1975 centred around advances in fibre technology for telecommunications. This year’s hottest topic was undoubtedly optical interconnects for large-scale AI clusters.

Following an insightful plenary talk by Pradeep Sindhu from Microsoft on AI data centre architecture, sessions were packed in which co-packaged optics (CPO) and associated technologies were discussed. The excitement had been fueled by Nvidia’s earlier announcement of using co-packaged optics in its next generation of Ethernet and Infiniband switches.

The show floor featured 800 gigabit-per-second (Gbps), 1.6 terabit-per-second (Tbps), and the first 3.2Tbps interconnect demonstrations using different interface standards and technologies.

For access, 50G-PON was showcased in triple PON coexistence mode, while interest in next-generation very high-speed PON spurred the technical sessions.

Other standout topics included numerous papers on fibre sensing, stimulating discussions on optical satellite communications, and a post-deadline paper demonstrating unrepeated hollow-core fibre transmission over more than 200km.

OFC 2025 was fun too. When else do you get to reimagine communications after an alien attack, as in this year’s rump session?

No visit to San Francisco is complete without trying one of Waymo’s self-driving taxis. Having been proud of Dmitri Dolgov, Waymo’s CEO, for his plenary talk at OFC 2019, it was thrilling to see autonomous driving in action. I love technology!

Daryl Inniss, Omdia Consultant, Optical Components and Fibre Technologies

I worked on commercialising fibre technology for emerging applications at OFS – now Lightera – from 2016 to 2023. I spent the prior 15 years researching and analysing the optical components market.

Today, I see a market on the cusp of a transition due to the unabated bandwidth demand and the rise of computing architectures to support high-performance computing (HPC) and artificial intelligence (AI).

Even optical fibre, the fundamental optical communications building block, is under intense scrutiny to deliver performance suitable for the next 30 to 50 years. Options include hollow-core and multi-core fibre, two of the three fibre technologies that caught my attention at OFC 2025.

The third, polarisation-maintaining fibre arrays for co-package optics, is one part of the conference’s biggest story. OFC 2025 provided a status update on these technologies.

Hollow-core fibre

OFC’s first day hollow-core fibre workshop (S2A) illustrated its niche status and its potential to remain in this state until the fibre is standardised. The industry ecosystem was well represented at the session.

Not surprisingly, challenges highlighted and summarised by Russ Ellis, Microsoft’s Principal Cloud Network Engineer, included manufacturing, field installation, field splicing, cabling, and termination inside the data centre. These are all expected topics and well understood.

I was surprised to hear Microsoft report that the lack of an established ecosystem was a challenge, and I’ll explain why below.

Coming into OFC, the biggest market question was fibre manufacturing scalability, as most reported draws are 5km or less. Supplier YOFC put this concern to rest by showcasing a +20 km spool from a single fibre draw on the show floor. And Yingying Wang, CEO of Linfiber, reported that 50 to 100km preforms will be available this year.

In short, suppliers can scale hollow-core fibre production.

From a field performance perspective, Microsoft highlighted numerous deployments illustrating successful fibre manufacturing, cabling, splicing, termination, installation, and testing. The company also reported no field failures or outages for cables installed over five years ago.

However, to my knowledge, the hollow-core fibre ecosystem challenge is a consequence of a lack of standardisation and discussion about standardisation.

Each fibre vendor has a different fibre design and a different glass outer diameter. Microsoft’s lack-of-an-ecosystem comment mentioned above is therefore unsurprising. Only when the fibre is standardised can an ecosystem emerge, generating volumes and reducing costs,

Today, only vertically integrated players benefit from hollow-core fibre. Until the fibre is standardised, technology development and adoption will be stunted.

Multi-core fibre

I was pleasantly surprised to find multiple transceiver vendors showcasing modules with integrated fan-in/fan-out (FIFO). This is a good idea as it supports multi-core fibre adoption.

One vendor is targeting FR4 (TeraHop for 2x400G), while another is targeting DR8 (Hyper Photonix for 8x100G). There is a need to increase core density, and it is good to see these developments.

However, we are still very far from multi-core fibre commercialisation as numerous operational factors, for example, are impacted. The good news is that multi-core fibre standardisation is progressing.

Polarisation-maintaining fibre

According to Nick Psaila, Intel’s principal engineer and technology development manager, polarisation-maintaining fibre arrays remain expensive.

The comment was made at Optica’s February online Industry Meeting and verified in my follow-up conversation with Psaila.

Using an external laser source is the leading approach to deliver light for co-packaged optics, highlighting an opportunity for high-volume, low-cost polarisation-maintaining fibre arrays.

Co-packaged optics were undoubtedly the most significant topic of the show.

Coherent showcased a 3Tbps concept product of VCSELs to be used in co-packaged optics. Given that multimode fibre is used in the shortest optical connections in data centres and that VCSELs have very low power consumption, I’m surprised I’ve not heard more about their use for this application.

Testing of emerging photonic solutions for HPC and AI devices has been identified as a bottleneck. Quantifi Photonics has taken on this challenge. The company introduced an oscilloscope that provided quality results comparable to industry-leading ones and is designed for parallel measurements. It targets photonic devices being designed for co-packaged optics applications.

Multiple channels, each with wavelength-division multiplexing lasers, must be tested in addition to all the electrical channels. This is time-consuming, expensive process, particularly using existing equipment.

Polymer modulators continue to be interesting because they have high bandwidth and the potential to be inexpensive. However, reliability is their challenge. Another vendor, NLM Photonics, is targeting this application.

The many vendors offering optical circuit switches was a surprising development. I wonder if this opportunity is sufficiently large to justify the number of vendors. I’m told that numerous internet content providers are interested in the technology. Moreover, these switches may be adopted in telecom networks. This is a topic that needs continual attention, specifically regarding the requirements based on the application.

Lastly, Lightmatter provided a clear description of its technology. An important factor is the optical interposer that removes input-output connectivity from the chip’s edge, thereby overcoming bandwidth limitations.

I was surprised to learn that the laser is the company’s design, although Lightmatter has yet to reveal more.

Avicena partners with TSMC to make its microLED links

TSMC, the leading semiconductor foundry, will make the photo-detectors used for Avicena Tech’s microLED optical interconnect technology.

Avicena is developing an optical interface that uses hundreds of parallel fibre links – each link comprising a tiny LED tranmitter and a silicon photo-detector receiver – to deliver terabit-per-second (Tbps) data transfers.

Avicena is targeting its microLED-based interconnect, dubbed LightBundle, for artifical intelligence (AI) and high-performance computing (HPC) applications.

The deal is a notable step for Avicena, aligning its technology with TSMC’s CMOS manufacturing prowess. The partnership will enable Avicena to transition its technology from in-house prototyping to high-volume production.

Visible-light technology

Avicena’s interconnects operate in the visible light spectrum at 425-430nm (blue light), differing from the near-infrared used by silicon photonics. The lower wavelength band enables simpler photo-detector designs where silicon efficiently absorbs blue light.

“Silicon is a very good detector material because the absorption length at that kind of wavelength is less than a micron,” says Christoph Pfistner, vice president of sales and marketing at Avicena. “You don’t need any complicated doping with germanium or other materials required for infrared detectors.”

Visible-light detectors can therefore be made using CMOS processes. For advanced CMOS nodes, however, such as used to make AI chips, hybrid bonding is required with a separate photo-detector wafer.

TSMC is adapting its CMOS Image Sensor (CIS) process used for digital cameras that operate in the megahertz range, to support Avicena’s photo-detectors that must work in the gigahertz range.

For the transmitter, Avicena uses gallium nitride-based microLEDs developed for the micro-display industry, paired with CMOS driver chips. Osram is Avicena’s volume LED supplier.

Osram has adapted its LED technology for high-speed communications and TSMC is now doing the same for the photo-detectors, enabling Avicena to mass produce its technology.

Specifications

The LED is used to transmit non-return-to-zero (NRZ) signalling at 3.5 to 4 gigabit-per-second (Gbps). Some 300 lanes are used to send the 800 gigabit data payload, clock, and associated overhead bits.

For the transmitter, a CMOS driver modulates the microLED while the receiver comprises a photo-detector, a trans-impedance amplifier (TIA) and a limiting amplifier.

By operating in this ‘slow and wide’ manner, the power consumption of less than 1 picojoule-per-bit (pJ/b) is achievable across 10m of the multi-mode fibre bundle. This compares to 3-5pJ/b using silicon photonics and up to 20pJ/b for optical pluggable transceivers though the latter support longer reaches.

The microLED links achieve a bandwidth density of over 1 terabit/mm and Avicena says this can be improved. Since the design is a 2D array, it is possible to extend the link density in area (in 2D) and not be confined to the ‘beachfront’ stretch. But this will be within certain limits, qualifies Pfistner

Applications

A key theme at the recent OFC 2025 show was optical interconnect options to linearly scale AI processing performance by adding more accelerator chips, referred to as the scale-up architecture.

At present copper links are used to scale up accelerators but the consensus is that, at some point, optics will be needed once the speed-distance performance of copper is exceeded. Nvidia’s roadmap suggests that copper can still support larger scale-up architectures for at least a couple of graphics processing unit (GPU) generations yet.

Avicena is first targeting its microLED technology in the form of an optical engine to address 1.6Tbps on-board optics modules. The same optical engine can also be used in active optical cables.

The company also plans to use its optical engine for co-packaged optics, and for in-package interconnect applications using a die-to-die (D2D) electrical interface such as the Universal Chiplet Interconnect Express (UCIe) or the OCP’s Bunch of Wires (BOW) interface. On-board optics, also known as co-packaged optics, refers to optics on a separate substrate close to the host ASIC, with both packaged together.

One such application for in-packaged optics is memory disaggregation involving high-bandwidth memory (HBM). “There’s definitely more and more interest in what some people refer to as optical HBM,” says Pfistner. He expects initial deployment of optical HBM in the 2029-2030 timeframe.

The foundry TSMC is also active in silicon photonics, developing the technology as part of its advanced system-in-package technology roadmap. While it is early days, Avicena’s microLED LightBundle technology could become part of TSMC’s optical offerings for applications such as die-to-die, xPU-to-memory, and in-packaged optics.

OFC: After the aliens, a decade to rewire the Earth

At the OFC 2025 Rump Session, held in San Francisco, three teams were set a weighty challenge. If a catastrophic event—a visit by aliens —caused the destruction of the global telecommunications network, how would each team’s ‘superheroes’ go about designing the replacement network? What technologies would they use? And what issues must be considered?

The Rump Session tackled a provocative thought experiment. If the Earth’s entire communication infrastructure vanished overnight, how would the teams go about rebuilding it?

Twelve experts – eleven from industry and one academic – were split into three teams.

The teams were given ten years to build their vision network. A decade was chosen as it is a pragmatic timescale and would allow the teams to consider using emerging technologies.

The Rump Session had four rounds, greater detail being added after each.

The first round outlined the teams’ high-level visions, followed by a round of architectures. Then a segment detailed technology, the round where the differences in the team’s proposals were most evident. The final round (Round 4), each team gave a closing statement before the audience chose the winning proposal.

The Rump Session mixed deep thinking with levity and was enjoyed by the participants and audience alike.

Round 1: Network vision

The session began with each team highlighting their network replacement vision.

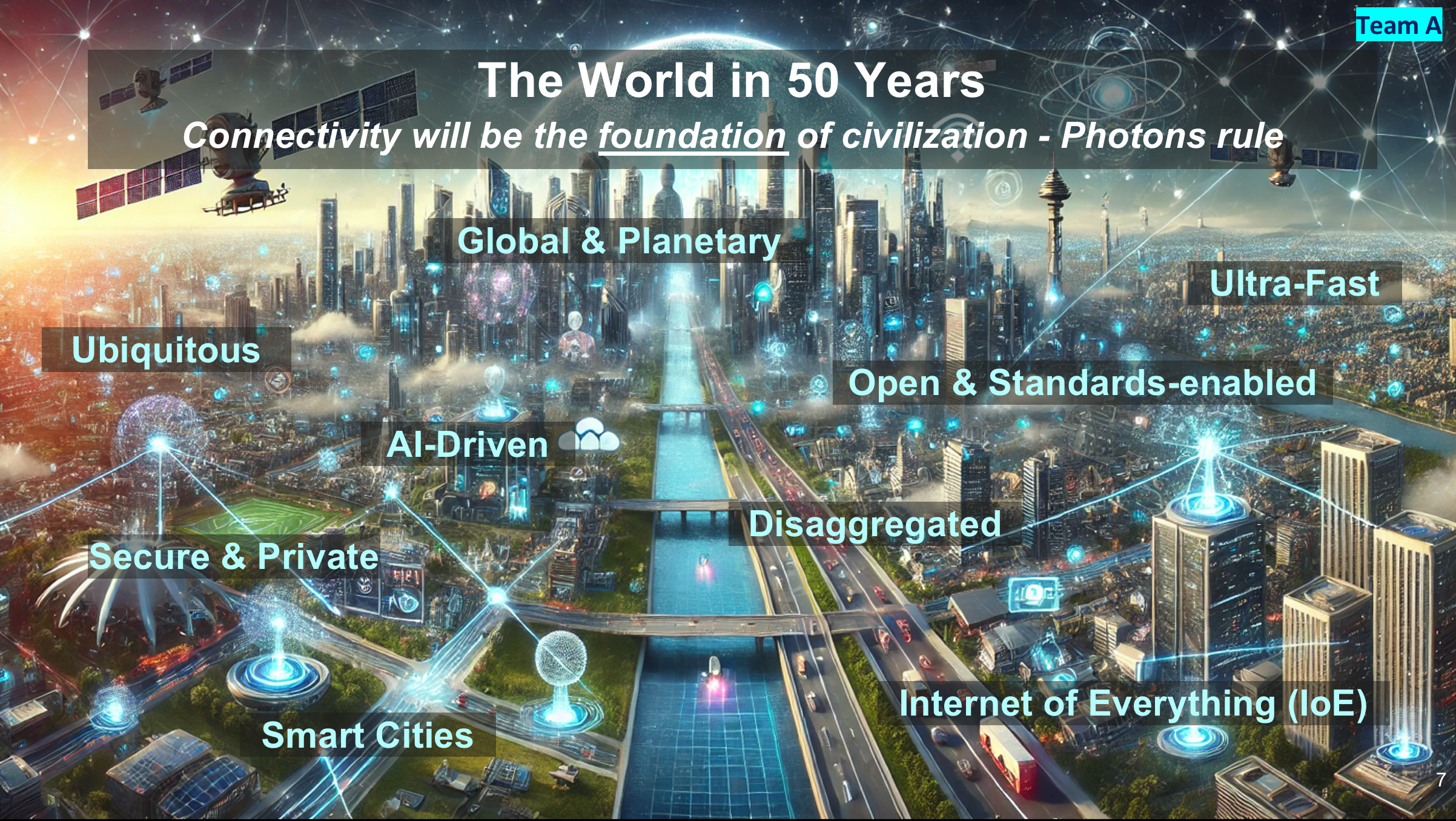

Team A’s Rebecca Schaevitz opened by looking across a hundred-year window. Looking back fifty years to 1975, networking and computing were all electrical, she said, telephone lines, mainframe computing, radio and satellite.

Schaevitz said that by 2075, fifty years hence, connectivity will be the foundation of civilisation. The key difference between the networks a century apart is the marked transition from electrons to photons.

In the future vision, everything will be connected—clothes, homes, roads, even human brains—using sensors and added intelligence. As for work, offices will be replaced with real-time interactive holograms (suggesting humanity will still be working in 2075).

Schaevitz then outlined what must be done in the coming decade to enable Team A’s Network 2075 vision.

The network’s backbone must be optical, supporting multiple wavelengths and quantum communications. Team A will complement the fixed infrastructure with terabit-speed wireless and satellite mega-constellations. And AI will enable the network to be self-healing and adaptive, ensuring no downtime.

Vijay Vusirikala outlined Team B’s network assumptions. Any new network will need to support the explosive growth in computing and communications while being energy constrained. “We must reinvent communications from the ground up for maximum energy savings,” said Visurikala.

But scarcity—in this case energy—spurs creativity. The goal is to achieve 1000x more capacity for the same energy demand.

The network will have distributed computing based on mega data centres and edge client computing. Massive bandwidth will be made available to link humans and to link machines. Lastly, just enough standardisation will be used for streamlined networking.

Team C’s Katharine Schmidtke closed the network vision round. The goal is universal and cheap communications, with lots of fibre deployed to achieve this.

The emphasis will be on creating a unified fixed-mobile network to aid quick deployment and a unified fibre-radio spectrum for ample connectivity.

Team C stressed the importance of getting the network up and running by using a modular network node. It also argued for micro data centres to deliver computing close to end users.

Global funding will be needed for the infrastructure rebuild, and unlimited rights of way will be a must. Unconstrained equipment and labour will be used at all layers of the network.

Team C will also define the communication network using one infrastructure standard for interoperability. One audience member questioned the wisdom of a tiny committee alone specifying such a grand global project.

The network will also be sustainable by recycling the heat from data centres for crop production and supporting local communities.

Round 2: Architectures

Team A’s Tad Hofmeister opened Round 2 by saying what must change: the era of copper will end – no copper landlines will be installed. The network will also only use packet switching, no more circuit switch technology. And IPv4 will be retired (to great cheering from the audience).

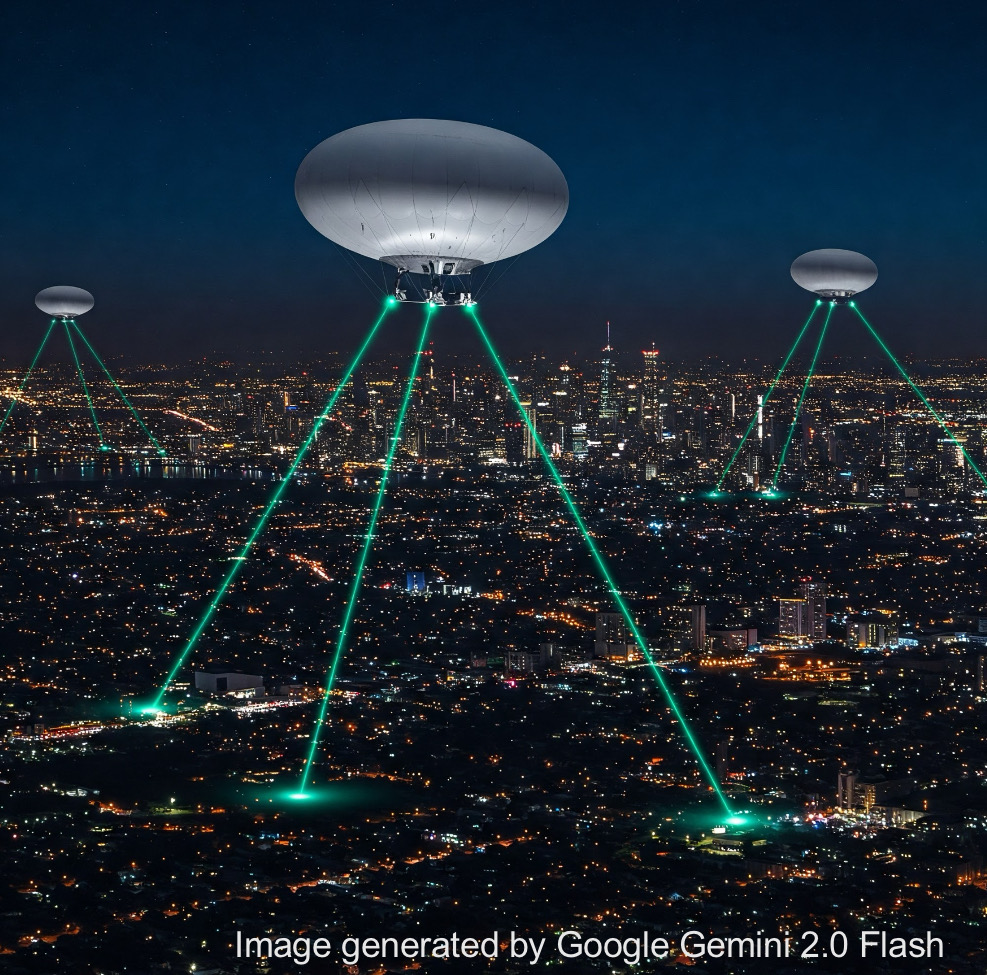

Team A also proposed a staged deployment. First, a network of airborne balloons will communicate with smartphones and laptops, which will be connected to the ground using free-space optical links.

Stage 2 will add base stations complemented with satellite communications. Fibre will be deployed on a massive scale along roads, railways, and public infrastructure.

Hofmeister stressed the idea of the network being open and disaggregated with resiliency and security integral to the design.

There will be no single mega-telecom or hyperscaler; instead, multiple networks and providers will be encouraged. To ensure interoperability, the standards will be universal.

Security will be based on a user’s DNA key. What about twins? asked an audience member. Hofmeister had that covered: time-of-birth data will be included.

Professor Polina Bayvel detailed Team B’s architectural design. Here, packet and circuit switching is proposed to minimise energy/bit/ km. It will be a network with super high bandwidths, including spokes of capacity extending from massive data centres connecting population centres.

Bayvel argued the case for underwater data centres: 15 per cent of the population live near the coast, she said, and an upside would be that people could work from the beach.

Team C’s Glenn Wellbrock proposed unleashing as much bandwidth as possible by freeing up the radio spectrum and laying hollow-core fibre to offer as much capacity as possible.

Wellbrock views hollow-core fibre as a key optical communications technology that promises years of development, just like first erbium-doped fibre amplifiers (EDFAs) and then coherent optics technology have done.

Team C showed a hierarchical networking diagram mapped onto the geography of the US – similar to today’s network – with 10s of nodes for the wide area network, 100s of metropolitan networks, and 10,000s of access nodes.

Wellbrock proposes self-container edge nodes based on standardised hardware to deliver high-speed wireless (using the freed-up radio spectrum) and fibre access. There would also be shared communal hardware, though service providers could add their own infrastructure. Differentiation would be based on services.

AI would provide the brains for network operations, with expert staff providing the initial training.

Round 3: Technologies

Round 3, the enabling technologies for the new network, revealed the teams’ deeper thinking.

Team A’s Chris Doerr advocated streamlining and pragmatism to ensure rapid deployment. Silicon photonics will make a quick, massive-scale, and economic deployment of optics possible. Doerr also favours massive parallelism based on 200 gigabaud on-off keying (not PAM-4 signalling). With co-packaged optics added to chips, such parallel optical input-output and symbol rate will save significant power.

Standards for all aspects of networking will be designed first. Direct detection will be used inside the data centre; coherent digital signal processing will be used everywhere else. More radically, in the first five years, all generated intellectual property regarding series, converters, modems, and switch silicon will be made available to all competition. Chips will be assembled using chiplets.

For line systems, C-band only followed by the deployment of Vibranium-doped optical amplifiers (Grok 3 gives a convincing list of the hypothetical benefits of VDFAs). Parallelism will also play a role here, with spatial division multiplexing preferred to combining a fibre’s O, S, C and L bands.

Like Team C, Doerr also wants vast amounts of hollow-core fibre. It may cost more, but the benefits will be long-term, he said.

Peter Winzer (Team B) also argued for parallelism and a rethink in optics: the best ‘optical’ network may not be ‘optical’ given that photons get more expensive the higher the carrier frequency. So, inside the data centre, using the terahertz band and guided-wave wire promises 100x energy per bit benefits compared to using O-band or C-band optics.

Winzer also argues for 1000x more energy-efficient backbone connectivity by moving to 10-micron wavelengths and ultra-wideband operation to compensate for the 10x spectral efficiency loss that results. But for this to work, lots of fibre will be needed. Here, hollow-core fibre is a possible option.

Chris Cole brought the round to a close with radical ways to get the networking deployed. He mentioned Meta’s Bombyx, an installation machine that spins compact fibre cables along power lines.

Underground cabling would use nuclear fibre boring (including the patent number) which produces so much heat that it bores a tunnel while lining its walls with the molten material it produces. An egg-shaped portable nuclear reactor to power data centre containers was also proposed.

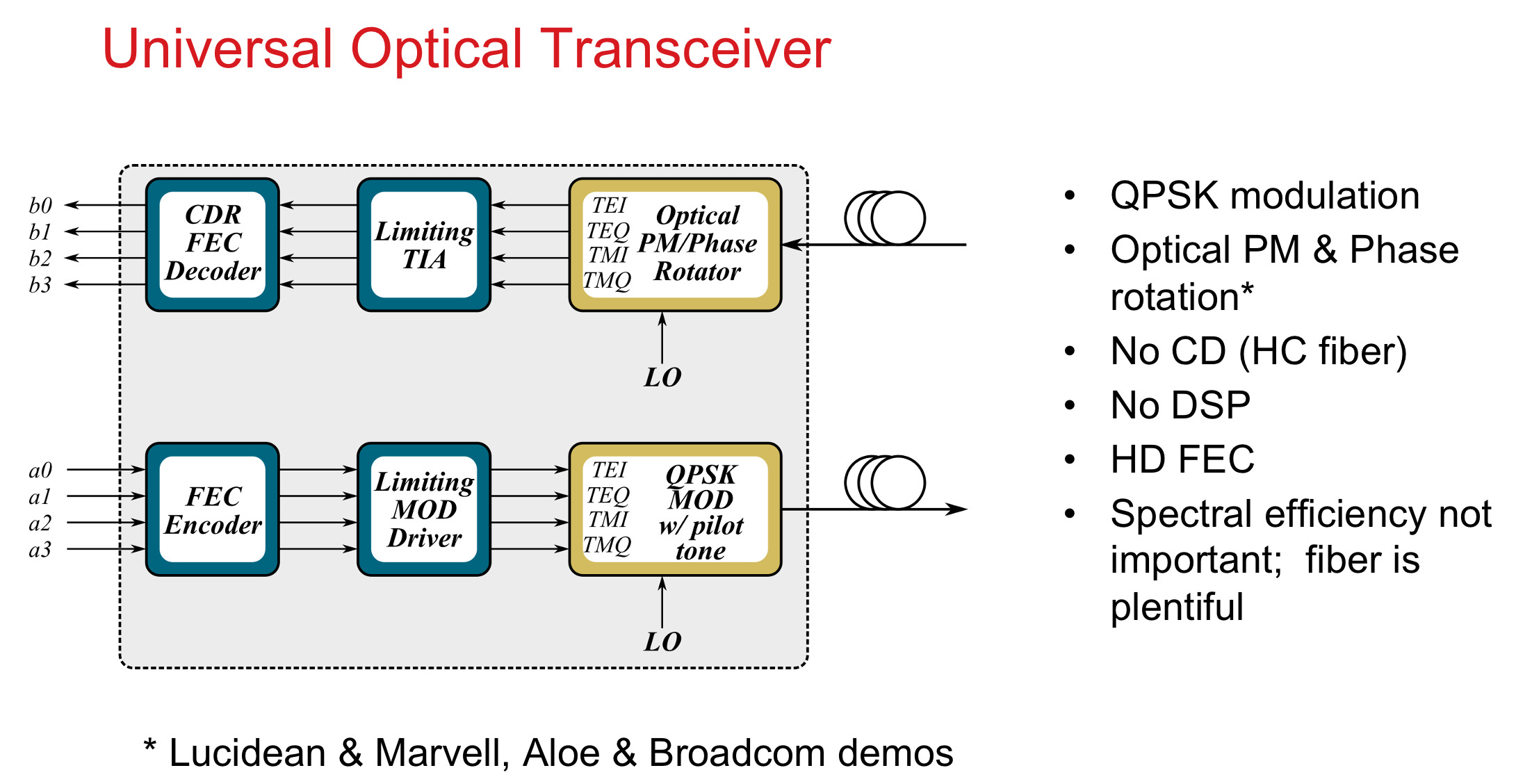

Cole defined a ‘universal’ transceiver with quadruple phase-shift keying (QPSK) modulation with no digital signal processing. “Spectral efficiency is not important as fibre will be plentiful,” says Cole.

Completing arguments

After each team had spent a total of some 14 minutes outlining their networks, they were given one more round for final statements.

Maxim Kuschnerov expanded on the team’s first-round slide, which outlined the ingredients needed to enable its Network 2075 vision. He also argued that every network element and connected device should be part of a global AI network. And AI will help co-design the new access network.

The new network will enable a massive wave of intelligent devices. Data will be kept at the edge, and the network will enable low-latency communications and inferencing at the edge.

Team B’s Dave Welch outlined some key statements: fusion energy will power the data centres with 80 per cent of the energy recycled from the heat. Transistors will pass the 10THz barrier, there will be 1000x scaling for the same energy, and an era of atto-joules/bit will begin. “And human-to-human interactions will still make the world go round,” says Welch.

Team C’s Jörg-Peter Elbers ended the evening presentations by outlining schemes to enable the new network: high-altitude platforms in a mega constellation (20km up) trailing fibre to the ground.

Such fibres and free-space links would also act as a sensing early-warning system in case the aliens returned.

Lastly, Elbers suggested we all get a towel (an important multi-purpose tool as outlined in Douglas Adams’ The Hitchhiker’s Guide to the Galaxy). A towel can be used for hand-to-hand combat (when wet), ward off noxious fumes, and help avoid the gaze of the Ravenous Bugblatter beast of Traal. Lastly, and in the spirit of the evening, if all else fails, a towel can be used for sending line-of-sight, low-bandwidth smoke signals.

Team C ended the presentations by throwing towels into the audience, like tennis stars after a match.

Common threads

All the teams agreed that fibre was necessary for the network backbone, with hollow-core fibre widely touted.

Two of the teams emphasised a staged rollout and all outlined ways to avoid the ills of existing legacy networks.

Differences included using satellites rather than fibre-fed high-altitude balloons, which are quicker and cheaper to deploy, and the idea of container edges rather than a more centralised service edge. All the teams were creative with their technological approaches.

What wasn’t discussed – it wasn’t in the remit – was the impact of a global disconnect on the world’s population. We would suddenly become broadband have-nots for several years, disconnected from smartphones and hours-per-day screen time.

The teams’ logical assumption was to get the network up and running with even greater bandwidth in the future. But would gaining online access after years offline change our habits? Would we be much more precious in using our upload and download bits? And what impact would a global comms disconnect have on society? Would we become more sociable? Would letter-writing become popular again? And would local communities be strengthened?

Maxim Kuschnerov came closest to this when, in his summary talk, he spoke about how the following iteration of network and communications should be designed to be a force for good for humanity and for its economic prospects.

Team winners

The audience chose Team B’s network proposal. However, the choice was controversial.

An online voting scheme, which would have allowed users to vote and change their vote as the session progressed, worked perfectly, but keeled over on the night.

The organisers’ fallback plan, measuring the decibel level of the audience’s cheers for each team, ended in controversy.

First, not all the Session attendees were present at the end. Second, a couple of the participants were seen self-cheering into a microphone. Evidence, if needed, as to the seriousness the ‘superheroes’ embraced architecting a new global network.

“It has been an evening of pure creative chaos: the more time I spend reflecting on the generated ideas, the more their value increases to me,” says Antonio Tartaglia of Ericsson, one of the organisers. “The voting chaos has been an act of God, because all three teams deserved to win.”

Tartaglia came up with this year’s theme for the Rump Session.

“Rump sessions are all about creative debate, and this year’s event took that to its full potential,” says Dirk van den Borne of Juniper Networks, another of the organisers. “Micro data centres, fibre-tethered balloons, Terahertz waveguides, and communication by pigeon; the sheer breath of ideas shows what an exciting and inventive industry we’re working in.”

The evening ended with a tribute to Team C’s Glenn Wellbrock. BT’s Professor Andrew Lord acknowledged Wellbrock’s career and contribution to optical communications.

Wellbrock officially retired days before the Rump Session.

Silicon photonics grapples with 3D packaging demands

Hesham Taha (pictured), CEO of start-up Teramount, is more upbeat about silicon photonics than ever. But, as he outlines, challenges remain.

Hesham Taha is putting in the miles. The CEO of Teramount has been travelling to the East and West to meet with companies.

Termount is working closely with customers and partners adopting its technology that adds fibre to silicon photonics chips.

“We’re shipping units to customers and partners, and we need to be close to them as they integrate our components and address the challenges of integration,” says Taha.

Teramount

For Taha, connecting fibre to a silicon photonics chip inside a pluggable optical transceiver is relatively straightforward.

Far more challenging is when the optical engine and chip are packaged together, known as co-packaged optics. Such a tight coupling raises reliability challenges.

The optical engine is close to the large, heat-generating chip, introducing manufacturing and reliability issues. Also, the fibre-connect to the optical engine inside the package must be scalable. Scaling is key because with each chip generation – whether an AI accelerator or a switch chip – the input-output (I/O) requirements grow.

Teramount’s technology couples the fibre to the silicon photonics chip using a photonic plug and photonic bump.

The photonic plug holds the fibres and couples them to the silicon photonics chip via a photonic bump, a component made during the silicon photonics wafer’s processing.

The photonic bump has two elements: a wideband deflector and a lens mirror for beam expansion. Expanding the light beam enables larger assembly tolerances.

The resulting wafer-level manufacturing may be more complicated, says Taha, but the benefits include relaxed tolerances in the assembly, wideband surface coupling, and the testing of the wafer and the die.

The photonic bump-and-plug combination also enables detachable optics for co-packaged optics designs, benefitting their manufacturing. (For more about Teramount’s technology, click here)

Silicon Photonics meets semiconductor thinking

Taha sees silicon photonics as a platform that enables the integration of optical functions at the wafer scale using standard semiconductor manufacturing techniques.

“It [silicon photonics design] has the same way of thinking as semiconductor people: chip designers, foundries, and packaging people,” says Taha. The result is that silicon photonics is bringing optics to chip design.

The growing maturity of the technology, and the emergence of foundries such as TSMC, GlobalFoundries, Tower Semiconductor, Intel, and ST Microelectronics offering silicon photonics, means that companies with photonic designs can be fabless; a model that has benefitted the chip industry.

Photonic chip designers can use a large foundry’s process design kit (PDK) and send off their silicon photonics designs to be manufactured in volume.

As for co-packaged optics, Taha sees it as a key in the evolution of silicon photonics. Co-package optics is the realisation of silicon photonics whereby optics is integrated next to advanced semiconductor chips.

Industry developments

The growing interest in silicon photonic and co-packaged optics is also evident in some recent announcements, driven by the AI compute scaling needs.

ST Microelectronics unveiled its 300mm wafer PIC100 silicon photonics technology. ST Microelectronics was active in silicon photonics 10 years ago and has returned due to the AI opportunity.

Marvell announced it offers a co-packaged optics solution for accelerator chips to address scale-up networking for AI architectures.

Leading foundry TSMC has outlined its silicon photonics roadmap, which includes co-packaged optics.

And at the GTC 2025 AI developers conference, Nvidia announced it is adding co-packaged optics to its switch platforms for scale-out networking.

“All this is not a surprise because this is where we expected silicon photonics to be one day when we founded the company 10 years ago,” says Taha. “It is just that this day is happening now.”

Teramount sees its fibre attach product as a part of an emerging ecosystem to enable standard semiconductor high-volume manufacturing.

This ecosystem comprises chip designers, foundries, OSATs [outsourced semiconductor assembly and test service providers], and system integrators.

But there are challenges. There may be wafer-scale manufacturing, but issues remain on the integration-packaging side.

“This is why we need to travel, to align with the different partners,” says Taha.

Challenges

Teramount is seeing challenges first-hand given its fibre-attach vantage point. Taha also highlights commercial issues still to be resolved.

The technical challenges revolve around integrating the silicon photonics die with the accompanying lasers and fibres in an advanced package.

Unlike a traditional pluggable optical transceiver, the silicon photonics chip is inserted in a hot environment and must meet operational temperatures of 85oC and even 105oC.

Multiple reflow soldering steps during manufacturing expose the packaging to even higher temperatures (270oC) and thermal stresses.

“These are new technical challenges that silicon photonic chip integration must meet 3D packaging requirements,” says Taha.

3D packaging has requirements that affect the fibre attach. For example, the silicon photonics chip is thinner than the die used in a pluggable if through-silicon via (TSV) technology is used.

TSV refers to the way a vertical electrical connector is done that passes through the die. Any mechanical stresses or warpage impacts the resulting optical performance of the die.

“Co-package optics is creating new challenges when connecting fibre to such thinner chips,” says Taha.

There are also issues with testing a design. “There are still no mature solutions for parallel optical and electrical testing,” says Taha.

The commercial issue he highlights centres around design ownership. With a pluggable module, all the components are delivered in one assembled device with one owner – the module maker.

With co-packaged optics, there are several stages of assembly, with components coming from multiple sources. “Who owns it?” says Taha.

Box system integrators making servers, switches, and the like don’t work with fibre. In contrast, co-packaged optics require connecting and managing hundreds of fibres that fit in a tight space. Good optical coupling and performance are a must to ensure the overall design.

“So this flow [for co-package optics] has yet to be set,” says Taha.

He says all the players, chip designers, foundry packaging vendors (OSATs), and system integrators still need to be aligned. That said, the industry, particularly the large silicon chip vendors, are working to make it happen, says Taha.

This implies that companies such as Nvidia, Intel, AMD, Broadcom, and Marvell are playing a key role here.

Given how the emerging AI opportunity is driving their chip businesses, they have every reason to make this work.

Cloud and AI: Opportunities that must be grabbed

The founder of Cloud Light, Dennis Tong, talks about the company, how its sale to Lumentum came about, and the promise of cloud and AI markets for optics.

For Dennis Tong (pictured), Hong Kong is a unique place that has a perfect blend of the East and West.

Tong, the founder and CEO of optical module specialist Cloud Light, should know. The company is headquartered in Hong Kong and has R&D offices in Hong Kong and Taipei, Taiwan. Cloud Light also has manufacturing sites in Asia: in the Chinese city of Dongguan—two hours by car, north of Hong Kong—and in the Philippines.

Now, Cloud Light is part of Lumentum. The U.S. photonics firm bought the optical module maker for $750 million in November 2023.

Tie-up

Cloud Light is a volume manufacturer of optical modules. The company takes 12-inch silicon photonic wafers, tests the wafers’ dies, and packages them for use in optical modules.

Cloud Light has a long relationship with Lumentum, using the U.S. company’s continuous-wave lasers for its silicon photonic-based optical modules.

Tong says he has been in photonics for 30 years and has good friends at Lumentum. “We had opportunities to chat and exchange views as to where the industry is going, and we shared a common vision,” he says. Eventually, the talk turned to a possible merger and acquisition.

Tong says the decision to sell the company centred on how best to grow the company. Cloud Light would have continued to do well, he says, but the company could grow much faster if he and his 1,600 staff joined Lumentum.

It is also timely. “Opportunities such as cloud and AI, they don’t come along very often,” says Tong.

Wafer-in, Product-out

Cloud Light has developed a manufacturing process dubbed “wafer-in, product-out.”

Turning a photonic integrated circuit (PIC) into a packaged optical module involves many stages and players. Designers of a PIC pass it to a foundry that results in the wafer. The wafer is shipped to an outsourced semiconductor assembly and test (OSAT) that does wafer back-end tasks: testing and dicing the wafer, and polishing. The working PICs—the known good dies—are shipped to a contract manufacturer that makes the pluggable modules.

“You can see that the entire collaboration chain is fragmented,” says Tong. “With our wafer-in, product-out process, we put everything in one group.”

Cloud Light takes the wafer from the foundry and does all the steps resulting in the delivered module.

Tong says the advantage of undertaking the complete process includes improved product yield. For example, the company measures coupling loss to the PIC and its optical waveguide loss during testing, and uses the insight to improve product yield.

Cloud Light has developed its own equipment to support automation. This know-how means that its design staff can work with the process and equipment colleagues to tailor the manufacturing process for new product designs. The precise assembly of unique micro-optics is one example.

It is this expertise and capability that particularly interested Lumentum in Cloud Light.

According to Tong, accumulating expertise in the different production areas has taken years: “There is a lot of subtlety to it, and we started to set this up in 2017.”

Hyperscaler business

Cloud Light succeeded early with a hyperscaler, making a 4×10-gigabit multimode VCSEL-based transceiver. But it soon realised market growth was coming from single-mode optical transceivers.

Its decision to pursue its wafer-in, product-out strategy stemmed from a desire to avoid becoming one of many single-mode optical transceiver makers. “We didn’t think we would add any value to the market by just creating a me-too company,” says Tong.

If the company was going to invest in a new platform, it would have to be scalable to support high volumes.

“It was very clear that silicon photonics was the right thing to do,” says Tong. “We were one of the first, if not the first, to launch a 400-gigabit silicon photonics-based transceiver in 2019.”

Cloud Light pitched its in-house scalable manufacturing approach to a hyperscaler that liked its plan, resulting in the company securing the hyperscaler as a customer.

Plans

Since the acquisition’s completion, Lumentum has given Cloud Light broad scope; there is no rush for full-blown integration, says Tong.

“Our mandate is to continue to grow the module business,” he says. “And we are open to using components from Lumentum and other suppliers.”

Lumentum’s components also offer Cloud Light the ability to create new products. “Customers are seeing us as more equipped, which opens up new, interesting opportunities,” says Tong.

Moreover, Cloud Light is not solely making modules for Lumentum. “The reality is that this is a very dynamic market, dominated by a few customers,” says Tong. “We are open to different business models as long as we can add value.”

Opportunities

At the time of the deal, Lumentum revealed that it expected Cloud Light would add $200 million plus to its yearly income. Cloud Light’s $200 million in revenues in the previous year was almost all from 400-gigabit and higher-speed transceiver sales.

Lumentum also makes coherent optical modems, ROADMs, and 3D sensing for commercial applications. Tong says coherent modules are one obvious opportunity for Cloud Light: “If you look into the future, I think the line between cloud/ datacom and telecom will become blurred.”

Cloud and AI will drive volumes, and the silicon photonics platform will be applicable for coherent modems as well. “So, a lot of the things that we have developed will also be applicable to coherent modules in the future,” says Tong. “And it is definitely applicable if one day coherent optics makes its way into the data centre.”

Coherent optics modules will keep increasing symbol rate and use more sophisticated coding schemes, but at some point, the effective data rate per line will start to plateau. To increase bandwidth beyond that, designs will go parallel by adding more channels. “Adding more fibre or more wavelengths, then it comes back to density, and then it’s all about packaging,” says Tong.

The ability to change its automated assembly for new applications also suggests that Cloud Light’s manufacturing capability could benefit Lumentum’s other product lines, such as ROADMs and even new markets such as optical circuit switches.

Co-packaged optics

Co-packaged optics are seen as one solution for applications where standard pluggable optics are no longer suitable.

Tong says that there are still issues before co-packaged optics are deployed at scale. One challenge is reliability; hyperscalars will not deploy the technology at scale until it has demonstrable good quality and reliability.

“The emergence of AI and cloud may accelerate that deployment, simply because of the volumes they are using and the density issue,” says Tong. Cost and thermal issues is also something co-packaged optics can address.

Cloud Light is ready for the advent of co-packaged optics. For its 800-gigabit transceiver, it can package a bare-die digital signal processor right next to the silicon photonics optical engine. “It’s not exactly a co-packaged optics product, but it has the same capability,” he says.

Shrinking lifecycles

The lifecycle of optical module products continues to shrink. At 10 gigabits, it was a decade-plus; for 100 gigabits, it was five to six years; at 400 gigabits, it has been more like three or four years. “Now, with AI, it is more like two to three years,” says Tong.

To be successful, it is all about time-to-market and time-to-scale.

“You need to be able to ramp up very quickly to the type of volumes and the type of quality that the customer is asking for,” says Tong. “There’s no time for you to get ready; you must be ready.”

The APC’s blueprint for silicon photonics

The Advanced Photonics Coalition (APC) wants to smooth the path for silicon photonics to become a high-volume manufacturing technology.

The organisation is talking to companies to tackle issues whose solutions will benefit the photonics technology.

The Advanced Photonics Coalition wants to act as an industry catalyst to prove technologies and reduce the risk associated with their development, says Jeffery Maki, Distinguished Engineer at Juniper Networks and a member of the Advanced Photonics Coalition’s board.

Origins

The Advanced Photonics Coalition was unveiled at the Photonic-Enabled Cloud Computing (PECC) Industry Summit jointly held with Optica last October.

The Coalition was formerly known as the Coalition for On-Board Optics (COBO), an industry initiative led by Microsoft.

Microsoft wanted a standard for on-board optics, until then it was a proprietary technology. At the time, on-board optics was seen as an important stepping stone between pluggable optical modules and their ultimate successor, co-packaged optics.

After years of work developing specifications and products, Microsoft chose not to adopt on-board optics in its data centres. Although COBO added other work activities, such as co-packaged optics, the organisation lost momentum and members.

Maki stresses that COBO always intended to tackle other work besides its on-board optics starting point.

Now, this is the Advanced Photonics Coalition’s goal: to have a broad remit to create working groups to address a range of issues.

Tackling technologies

Many standards organisations publish specifications but leave the implementation technologies to their member companies. In contrast, the Advanced Photonics Coalition is taking a technology focus. It wants to remove hurdles associated with silicon photonics to ease its adoption.

“Today, we see the artificial intelligence and machine learning opportunities growing, both in software and hardware,” says Maki. “We see a need in the coming years for more hardware and innovative solutions, especially in power, latency, and interconnects.”

Work Groups

In the past, systems vendors like Cisco or Juniper drove industry initiatives, and other companies fell in line. More recently, it was the hyperscalers that took on the role.

There is less of that now, says Maki: “We have a lot of companies with technologies and good ideas, but there is not a strong leadership.”

The Advanced Photonics Coalition wants to fill that void and address companies’ common concerns in critical areas. “Key customers will then see the value of, and be able to access, that standard or technology that’s then fostered,” says Maki.

The Advanced Photonics Coalition has yet to announce new working groups but it expects to do so in 2024.

One area of interest is silicon photonics foundries and their process design kits (PDKs). Each foundry has a PDK, made up of tools, models, and documentation, to help engineers with the design and manufacture of photonic integrated devices.

“A starting point might be support for more than one foundry in a multi-foundry PDK,” says Maki. “Perhaps a menu item to select the desired foundry where more than one foundry has been verified to support.”

Silicon photonics has long been promoted as a high-volume manufacturing technology for the optical industry. “But it is not if it has been siloed into separate efforts such that there is not that common volume,” says Maki.

Such a PDK effort would identify gaps that each foundry would need to fill. “The point is to provide for more than one foundry to be able to produce the item,” he says.

A company is also talking to the Advanced Photonics Coalition about co-packaged optics. The company has developed an advanced co-packaged optics solution, but it is proprietary.

“Even with a proprietary offering, one can make changes to improve market acceptance,” says Maki. The aim is to identify the areas of greatest contention and remedy them first, for example, the external laser source. “Opening that up to other suppliers through standards adoption, existing or new, is one possibility,” he says.

The Advanced Photonics Coalition is also exploring optical interconnecting definitions with companies. “How we do fibre-attached to silicon photonics, there’s a desire that there is standardisation to open up the market more,” says Maki. “That’s more surgical but still valuable.”

And there are discussions about a working group to address co-packaged optics for the radio access network (RAN). Ericsson is one company interested in co-packaged optics for the RAN. Another working group being discussed could tackle optical backplanes.

Maki says there are opportunities here to benefit the industry.

“Companies should understand that nothing is slowing them down or blocking them from doing something other than their ingenuity or their own time,” he says.

Status

COBO had 50 members earlier in 2023. Now, the membership listed on the website has dropped to 39 and the number could further dip; companies that joined for COBO may still decide to leave.

At the time of writing, an new as yet unannounced member has joined the Advanced Photonics Coalition, taking the membership to 40.

“Some of those companies that left, we think they will return once we get the working groups formed,” says Maki, who remains confident that the organisation will play an important industry role.

“Every time I have a conversation with a company about the status of the market and the needs that they see for the coming years, there’s good alignment amongst multiple companies,” he says.

There is an opportunity for an organisation to focus on the implementation aspects and the various technology platforms and bring more harmony to them, something other standards organisations don’t do, says Maki.

The status of silicon photonics - an ECOC interview

Daryl Inniss and I being interviewed at ECOC by Adtran’s Gareth Spence about the state of silicon photonics.

Click here for the interview.

The long arm of PCI Express

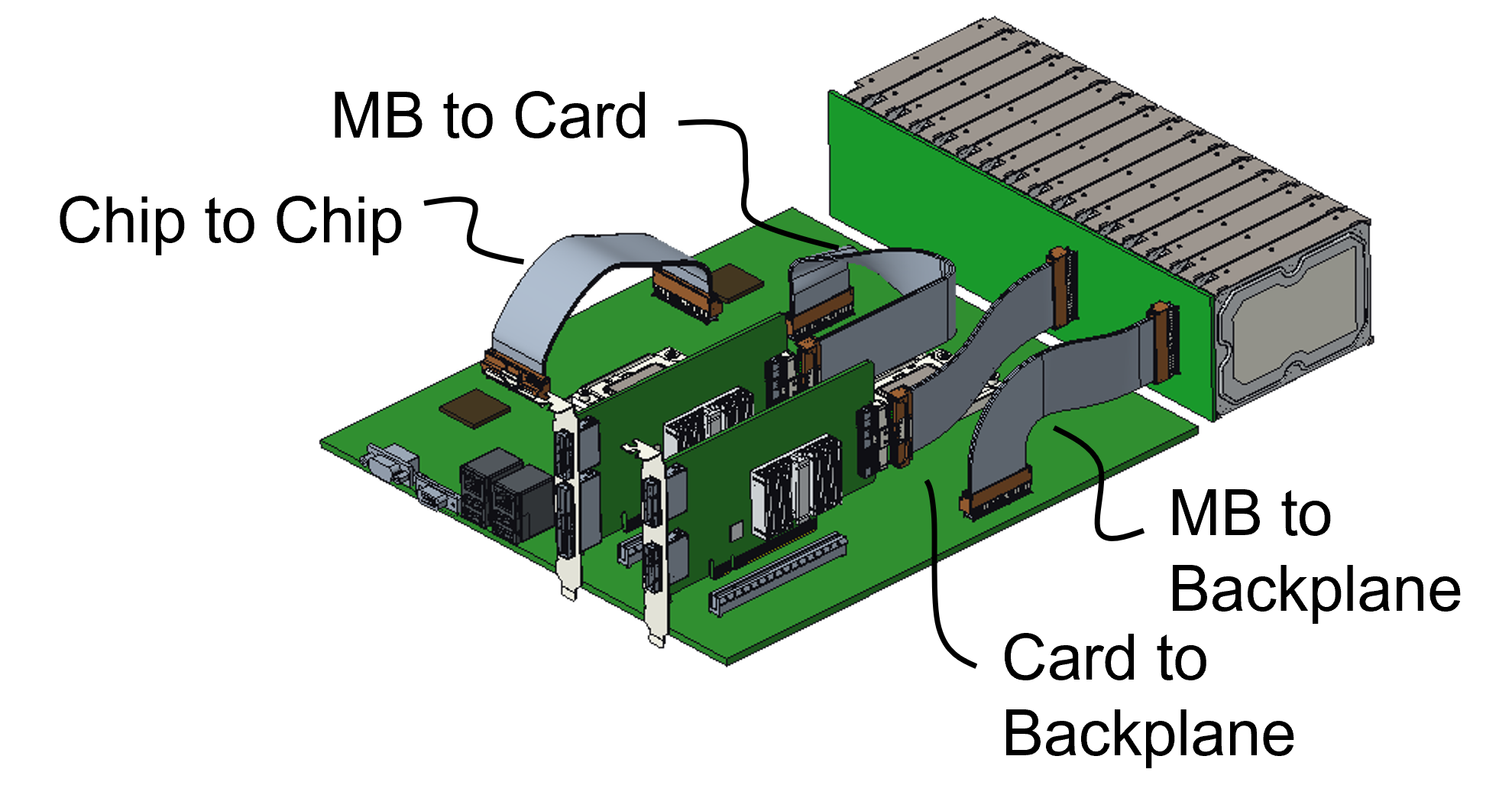

- Optical is being added as a second physical medium to the PCI Express (PCIe) data transfer protocol.

- PCI Express is an electrical standard, but now the Peripheral Component Interconnect Special Interest Group (PCI-SIG) has created a working group to standardise PCIe’s delivery optically.

- PCI-SIG is already developing copper cabling specifications for the PCI Express 5.0 and 6.0 standards.

Since each generation of PCIe doubles the data transfer rate, PCI-SIG member companies want copper cabling to help with the design of high-speed PCIe interconnects on a printed circuit board (PCB), between PCBs, and between racks (see diagram).

“We’ve seen a lot of interest over recent months for an optical cable that will support PCI Express,” says Al Yanes, PCI-SIG president and chairperson.

He cites the trends of the decreasing cost and size of optics and how silicon photonics enables the adding of optics alongside ASICs.

“We have formed a workgroup to deliver an optical cable,” says Yanes. “There are many applications, but one is a longer-distance reach for PCI Express.”

“It is a void in the market [the lack of optical support for PCIe], and it needs to be filled,” says Bill Koss, CEO of Drut Technologies. “These efforts tend to take longer than estimated, so better to start sooner.”

Drut has developed a PCIe over photonics solution as part of its photonic direct connect fabric for the data centre.

The data centre is going photonic, says Koss, so there is a need for such working standards as photonics get closer to processors.

The PCIe protocol

PCIe is used widely across many industries.

In the data centre, PCIe is used by general-purpose microprocessors and accelerator chips, such as FPGAs, graphics processing units and AI hardware, to connect to storage and network interface cards.

The PCIe bus uses point-to-point communications based on a simple duplex scheme – serial transmissions in both directions which is referred to as a lane.

The bus can be bundled in various lane configurations – x1, x2, x4, x8, x12, x16 and x32 – with x4, x8 and x16 the configurations most used.

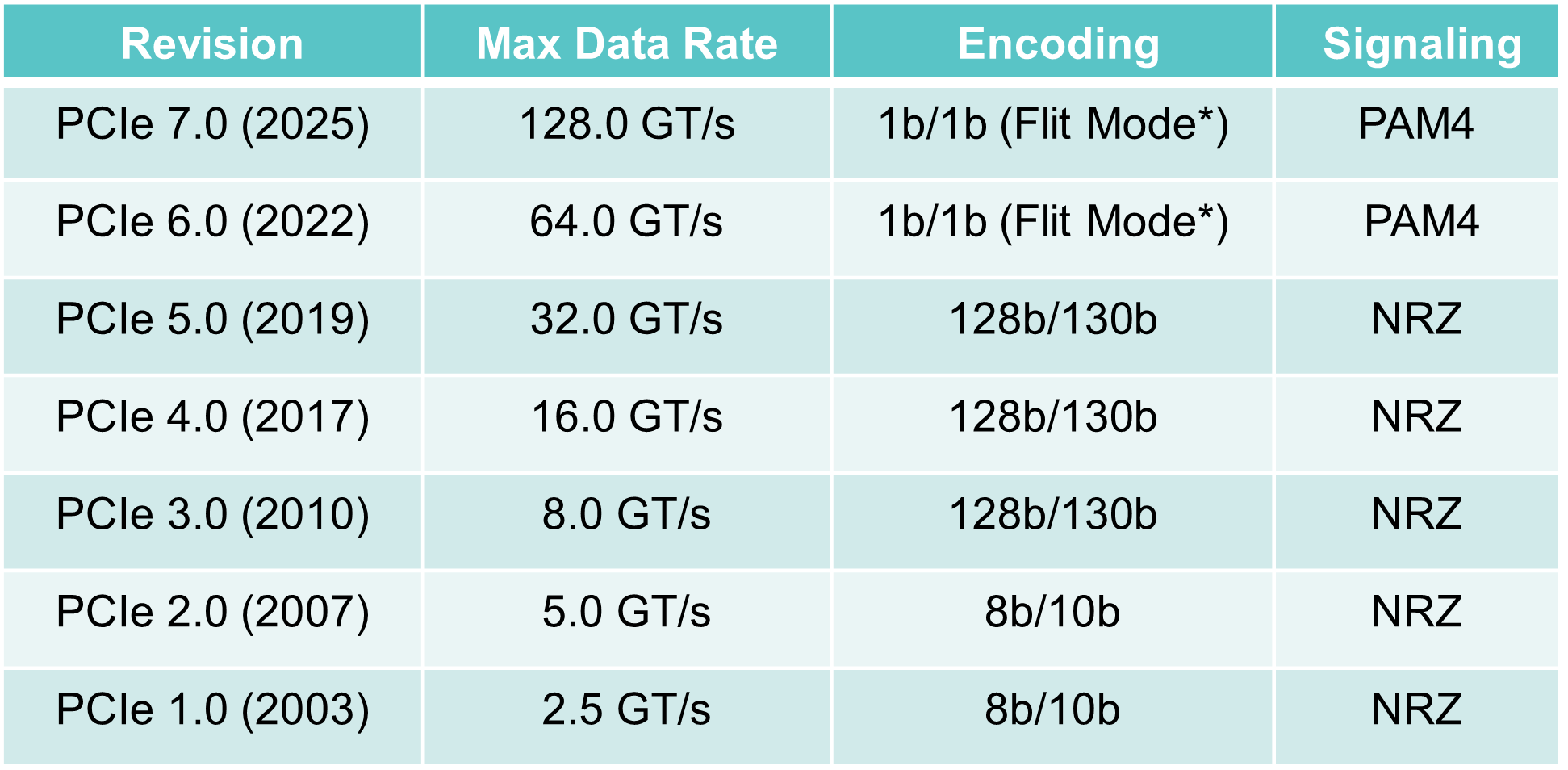

The first two PCIe versions, 1.0 and 2.0, delivered 2.5 and 5 giga transfers-per-second (GT/s) per lane per direction, respectively.

A transfer refers to an encoded bit. The first two PCIe versions use an 8b/10b encoding scheme such that for every ten-bit payload sent, 8 bits are data. This is why the data transfer rates per lane per direction are 2Gbps and 4Gbps (250 and 500 gigabytes per second), respectively.

With PCIe 3.0, the decision was made to increase the transfer rate to 8GT/s per lane, which assumed that no equalisation would be needed to counter inter-symbol interference at that speed. However, equalisation was required, which explains why PCIe 3.0 adopted 8GT/s and not 10GT/s.

Another PCIe 3.0 decision was to move to a 128b/130b scheme to reduce the encoding overhead from 20 per cent to over 1 per cent. Now the transfer and bit rates are almost equal from the PCIe 3.0 standard onwards.

PCIe 4.0 doubles the transfer rate from 8GT/s to 16GT/s, while PCIe 5.0 is 32GT/s per lane per direction.

Since then, PCIe 6.0 has been specified, supporting 64GT/s per lane per direction. PCIe 6.0 is the first standard for 4-level pulse amplitude modulation (PAM4) signalling.