Ethernet access switch chip boosts service support

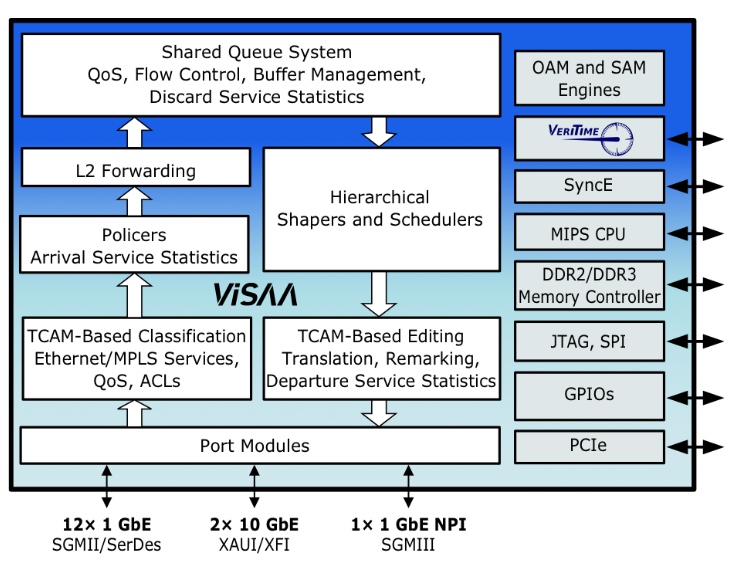

The Serval-2 architecture. Source: Vitesse

Vitesse Semiconductor has detailed its latest Carrier Ethernet access switch for mobile backhaul, cloud and enterprise services.

The Serval-2 chip broadens Vitesse's access switch offerings, adding 10 Gigabit Ethernet (GbE) ports while near-tripling the switching capacity to 32 Gigabit; the Serval-2 has 2x10 GbE and 12 1GbE ports.

The device features Vitesse's service aware architecture (ViSAA) that supports Carrier Ethernet 2.0 (CE 2.0). "We have built a hardware layer into the Ethernet itself which understands and can provision services," says Uday Mudoi, product marketing director at Vitesse.

CE 2.0, developed by the Metro Ethernet Forum (MEF), is designed to address evolving service requirements. First equipment supporting the technology was certified in January 2013. What CE 2.0 does not do is detail how services are implemented, says Mudoi. Such implementations are the work of the ITU, IETF and IEEE standard bodies with protocols such as Muti-Protocol Label Switching (MPLS)/ MPLS-Transport Profile (MPLS-TP) and provider bridging (Q-in-Q). "There is a full set of Carrier Ethernet networking protocols which comes on top of CE 2.0," says Mudoi.

Serval-2 switch

The Serval-2 switch features include 256 Ethernet virtual connections, hierarchical quality of service (QoS), provider bridging, and MPLS/ MPLS-TP.

An Ethernet Virtual Connection (EVC) is a logical representation of an Ethernet service, says Vitesse, a connection that an enterprise, data center or cell site uses to send traffic over the WAN.

Multiple EVCs can run on the same physical interface and can be point-to-point, point-to-multipoint, or multipoint-to-multipoint. Each EVC can have a bandwidth profile that specifies the committed information rate (CIR) and excess information rate (EIR) of the traffic transmitted to, or received from, the Ethernet service provider’s network.

The EVC also supports one or more classes of service and measurable QoS performance metrics. Such metrics include frame delay - latency - and frame loss to meet a particular application performance requirements.

The Serval-2 supports 256x8 class of service (CoS) EVCs, equivalent to over 4,000 bi-directional Ethernet services, says Mudoi.

The Serval-2 also supports per-EVC hierarchical queuing. It allows for 256 bi-directional EVCs with policing, statistics, and QoS guarantees for each CoS and EVC. Hierarchical QoS also enables a mix of any strict or byte-accurate weighting within the EVC, and supports the MEF's dual leaky bucket (DLB) algorithm that shapes traffic per-EVC and per-port.

"Service providers guarantee QoS to subscribers for the services that they buy," says Mudoi. "If each subscriber's traffic - even different applications per-subscriber - is treated using separate queues, then one subscriber's behavior does not impact the QoS of another." Supporting thousands of queues allows service providers to offer thousands of services, each with its own QoS.

Q-in-Q, defined in IEEE 802.1ad, allows for multiple VLAN headers - tags - to be inserted into a frame, says Mudoi, enabling service provider tags and customer tags.

Meanwhile, MPLS/ MPLS-TP direct data from one network node to the next based on shortest path labels rather than on long network addresses, thereby avoiding complex routing table look-ups. The labels identify virtual links between distant nodes rather than endpoints.

MPLS can encapsulate packets of various network protocols. Serval-2's MPLS-TP supports Label Edge Router (LER) with Ethernet pseudo-wires, Label Switch Router (LSR), and H-VPLS edge functions.

Q-in-Q in considered a basic networking function for enterprise and carrier networks, says Mudoi, while MPLS-TP is a more complex protocol.

Serval-2 also supports service activation and Vitesse's implementation of the IEEE 1588v2 timing standard, dubbed VeriTime.

"Before you provision a service, you need to run a test to make sure that once your service is provisioned, the user gets the required service level agreement," says Mudoi. Serval-2 supports the latest ITU-T Y.1564 service activation standard.

IEEE 1588v2 establishes accurate timing across a packet-based network and is used for such applications as mobile. The Serval-2 also benefits from Intellisec, Vitesse's MACsec Layer 2 security standard implementation (see Vitesse's Intellisec ).

"Both [Vitesse's VeriTime IEEE 1588v2 and Intellisec technologies] highly complement what we are doing in ViSAA," says Mudoi.

Availability

Serval-2 samples will be available in the third quarter of 2013. Vitesse expects it will take six months for system qualification such that Ethernet access devices using the chip and carrying live traffic are expected in the first half of 2014.

Fibre-to-the-NPU: optics reshapes the IP core router

Start-up Compass Electro-Optical Systems has announced an IP core router based on a chip with a Terabit-plus optical interface.

Asaf Somekh, vice president of marketing, showing Gazettabyte Compass-EOS's novel icPhotonics chip

Asaf Somekh, vice president of marketing, showing Gazettabyte Compass-EOS's novel icPhotonics chip

Having an optical interface linking directly to the chip, which includes a merchant network processor, simplifies the system design and enables router features such as real output queuing. The r10004 IP router is in production and is already deployed in an operator's network.

The company's icPhotonics chip integrates 168, 8 Gigabit VCSELs and 168 photodetectors for a bandwidth of 1.344 Terabit-per-second (Tbps) each direction. Eight of the chips are connected in a full mesh, doing away with the need for a router's switch fabric and mid-plane used to interconnect the router cards.

The resulting architecture saves power, space and cost, says Asaf Somekh, vice president of marketing at Compass-EOS. The start-up estimates that its platform's total cost of ownership over five years is a quarter to a third of existing IP core routers.

The high-bandwidth optical links will also be used to connect multiple platforms, enabling operators to add routing resources as required. Compass-EOS is coming to market with a 6U-high standalone platform but says it will scale up to 21 platforms to appear as one logical router.

The 800Gbps-capacity r10004 comes with 2x100 Gigabit-per-second (Gbps) and 20x10Gbps line cards options. The platform has real output queuing where all the input ports' packets are queued with quality of service applied prior to the exit port. The router also supports software-defined networking (SDN) that enables external control of traffic routing.

The company has its own clean room where it makes its optical interface. Compass-EOS has also developed its own ASICs and the router software for the r10004.

Somekh says developing the optical interface has been challenging, requiring years of development working with the Fraunhofer Institute and Tel-Aviv University. One challenge was developing a glue to fix the VCSELs on top of the silicon.

The start-up has raised US $120M with investors such as Cisco Systems, Deutsche Telekom and Comcast as well as several venture capitalist firms.

icPhotonics technology

Compass-EOS refers to its optical interface IC as silicon photonics but a more accurate description is integrated silicon-optics; silicon itself is not used as a medium for light. But its use of embedded optics to the chip has created a disruptive system.

The optical-interconnect addresses two chip design challenges: signal integrity for long transmission lengths and chip input/output (I/O).

With high-speed interfaces, achieving signal integrity across a high-speed line card and between boards is challenging. Routers use a midplane and switch fabric to connect the the router cards within a platform and parallel optics to connect chassis.

Compass-EOS has taken board-mounted optics one step further and integrated VCSELs and photodetectors to the packaged chip. This simplifies the platform by connecting cards using a mesh architecture, and allows scaling by linking systems.

The chip window shows the VCSELs and photodetectors Source: Compass-EOS

The chip window shows the VCSELs and photodetectors Source: Compass-EOS

The design also addresses chip I/O issues. "The I/O density is about 30x higher than traditional solutions and the gap will grow in future," says Somekh.

Directly attaching the optical interconnect to the CMOS chip overcomes limitations imposed by ball grid array and printed circuit board (PCB) technologies.

Typically data is routed from the host PCB to an ASIC via a ball grid array matrix which has a ball pitch of 0.8mm. Shrinking this further is non-trivial given PCB signal integrity issues. Moreover, each electrical serdes (serialiser/ deserialiser) for data I/O uses at least eight bumps (transmit, receive, signal and ground) occupying a cell of 3.2×1.6 mm. For a 10Gbps device the resulting duplex data density is 2Gbps/mm2, increasing to 5Gbps/mm2 if a 25Gbps device is used, according to Compass-EOS.

The start-up says its optical-interconnect achieves a chip I/O of 61Gbps/mm2. "This will increase to 243Gbps/mm2 once we move to 32Gbps."

The resulting design uses 10 percent of the total CMOS area for I/O. "This is a more efficient chip design," says Somekh. "Most of the silicon is used for logic tasks."

The serdes on chip still need to interface to hundreds of 8Gbps channels. And moving to 32Gbps will present a greater challenge. In comparison, silicon photonics promises to simplify the coupling of optics and electronics.

Another design challenge is that the VCSELs are co-packaged with a large chip consuming 30-50W and generating heat. The design needs to make sure that the operating temperature of the VCSELs is not affected by the heat from the chip.

This is another promised advantage of silicon photonics where the operating temperature of the optics and silicon are matched.

Analysts' perspective

Gazettabyte asked two analysts - IDC's Vernon Turner and ACG Research's Eve Griliches - about the significance of Compass-EOS's announcement. The analysts were also asked for their views on the router's modularity, the total cost of ownership claims, the support for SDN and real output queueing, and whether the platform will gain market share from the IP core router incumbents.

IDC

Vernon Turner, senior vice president & general manager enterprise computing, network, telecom, storage, consumer and infrastructure.

One of the hardest places to innovate in the ICT (information and communications technology) world is at or around the speed of light. Anytime you can make things run faster, the last hurdle tends to be the speed by which things travel over an optical network.

Therefore, to see something that changes the form factor of a network router and innovates at the interconnect speed, it may be able to disrupt a significant part of the network industry.

"Separating the interconnect with the physical building block is huge. It means that you scale the pieces that you need, when and where you want them; this is not just a repackaging announcement"

Building the capacity of a router as needed is great for service providers and large enterprises since you deploy capacity only as you need it. Second, by using a photonics interconnect, the speed and distance over which two devices can sit is enhanced greatly, changing the way one builds network infrastructures.

Separating the interconnect with the physical building block is huge. It means that you scale the pieces that you need, when and where you want them; this is not just a repackaging announcement.

Regarding the total-cost-of-ownership claims, if these are valid, they are of a magnitude that does fit into a 'disruptive innovation' class where it will deliver network services to an underserved market and create new network services markets.

SDN is the latest buzzword [regarding the router's support for SDN]. But it is the last part of the virtualised data centre as the compute and I/O have already been figured out. SDN is not new, but the need to separate the data plane from the control plane for the service provider industry means that they can begin to create network services through virtualisation without impacting the network performance, something that already happens in server and storage performance.

Existing core router vendors use their own ASIC designs as the last-stop differentiation, so to do this [as Compass-EOS has done] on merchant silicon could have wide implications on router commoditisation, or at least at a faster rate than current trends.

ACG Research

Eve Griliches, vice president of optical networking

As to the significance of the announcement, it is not huge in the scheme of things, but it does bring the optical component use of replacing a backplane to market earlier than what has been quoted to ACG Research.

"Virtual output queueing is a smart way to do quality of service"

In theory, the router should be a smaller footprint which results in better total cost of ownership due to the optical modules. The advantage with this optical patch-panel approach is that it allows a much higher bandwidth to cross the backplane which is now an optical interconnect. That means you don't have to do as much flow control, or drop as many packets, or keep the utilization of the router so low. You can bring up the utilisation rate from let's say 15 percent to maybe 25 percent or higher. All that results in lower total cost of ownership in theory.

SDN in a bit nebulous. Virtual output queueing is a smart way to do quality of service, but there are key software features like how many BGP (border gateway protocol) peers are supported, multicast capability, as well as signaling for MPLS (multiprotocol label switching), do they support RSVP-TE (resource reservation protocol - traffic engineering) or LDP (label distribution protocol)? Or both? Building a real router still takes years of work.

Faster interconnects are the way to go across routing and optical platforms, period. This [Compass-EOS platform] can help. Do I see this optical piece fitting nicely into an already existing router? Yes. I think if that doesn't happen, they will have a bit of an uphill battle nudging the incumbents.

On the other hand, if full router functionality is not needed at some junctures, as we've seen with the LSR (label switch router) technology, then they may have a place in the network. But operators don't like to play around with their routed network too much, so it may be greenfield application that are mostly available to them [Compass-EOS] initially.