Heterogeneous integration comes of age

Silicon photonics luminaries series

Interview 7: Professor John Bowers

August has been a notable month for John Bowers.

Juniper Networks announced its intention to acquire Aurrion, the US silicon photonics start-up that Bowers co-founded with Alexander Fang. And Intel, a company Bowers worked with on a hybrid integration laser-bonding technique, unveiled its first 100-gigabit silicon photonics transceivers.

Professor John BowersBower, a professor in the Department of Electrical and Computer Engineering at the University of California, Santa Barbara (UCSB), first started working in photonics in 1981 while at AT&T Bell Labs.

Professor John BowersBower, a professor in the Department of Electrical and Computer Engineering at the University of California, Santa Barbara (UCSB), first started working in photonics in 1981 while at AT&T Bell Labs.

When he became interested in silicon photonics, it still lacked a good modulator and laser. "If you don't have a laser and a modulator, or a directly modulated laser, it is not a very interesting chip,” says Bowers. "So I started thinking how to do that."

Bowers contacted Mario Paniccia, who headed Intel’s silicon photonics programme at the time, and said: “What if we can integrate a laser? I think there is a good way to do it.” The resulting approach, known as heterogeneous integration, is one that both Intel and Aurrion embraced and since developed.

This is a key Bowers trait, says Aurrion co-founder, Fang: he just knows what problems to work on.

"John came up with the concept of the hybrid laser very early on," says Fang. "Recall that, at that time, silicon photonics was viewed as nothing more than people making plasma-effect phase shifters and simple passive devices. John just cut to the chase and went after combining III-V materials with silicon."

If you look at the major companies with strong photonics activities, you’ll find a leader in that group that was developed under John’s training

Fang also highlights Bowers' management skills. “John can pick players and run teams,” says Fang, who describes himself as one of those privileged to graduate out of Bowers’ research group at UCSB.

“You find yourself in an environment where John picks a team of sharp folk with complementary skills and domain expertise to solve a problem that John determines as important and has some insight on how to solve it,” says Fang. “If we look like we are going to drive off the road, he nudges with a good mix of insight, fear, and humour.”

It has resulted in some of the best trained independent thinkers and leaders in the industry, says Fang: “If you look at the major companies with strong photonics activities, you’ll find a leader in that group that was developed under John’s training”.

Silicon photonics

Bowers defines silicon photonics as photonic devices on a silicon substrate fabricated in a CMOS facility.

“Silicon photonics is not about using silicon for everything; that misses the point,” says Bowers. “The key element is using silicon as a substrate - 12-inch wafers and not 2- or 3-inch wafers - and having all the process capability a modern silicon CMOS facility brings.” These capabilities include not just wafer processing but also advanced testing and packaging.

The world is about to change and I don't think people have quite figured that out

“If you go to an advanced packaging house, they don't do 6-inch wafers and I don't know of indium phosphide and gallium arsenide wafers larger than 6 inches,” says Bowers. “The only solution is to go to silicon; that is the revolution that hasn't happened yet but it is happening now.”

Bowers adds that everything Aurrion does, there is automated test along the way. "And I think you have others; Luxtera has done a great job as well at wafer-level test and packaging," he says. "The world is about to change and I don't think people have quite figured that out."

Working with Intel was an eye-opener for Bowers, especially the process controls it applies to chip-making.

“They worry about distributions and yields, and it is clear why there are seven billion transistors on a chip and that chip will yield,” says Bowers. “When you apply that to photonics, it will take it to a whole new level.” Indeed, Bowers foresees photonics transfering to silicon.

Bowers highlights the fairly complex chips now being developed using silicon photonics.

“We have done a 2D scanner - a 32-element phased array - something one could never do in optics unless it was integrated all on one chip,” he says. The phased-array chip comprises 160 elements and is physically quite large.

This is another benefit of using 12-inch silicon wafers and fabricating the circuits in a CMOS facility. “You are not going to cost-effectively do that in indium phosphide, which I've worked on for the last 30 years,” says Bowers.

Another complex device developed at UCSB is a 2.54-terabit network-on-a-chip. “This is a larger capacity than anyone has done on any substrate,” he says.

Infinera’s latest photonic integrated circuit (PIC), for example, has a transport capacity of up to 2.4 terabit-per-second. That said, Bowers stresses that the network-on-a-chip is a research presentation while Infinera’s PIC is a commercial device.

Heterogeneous integration

Heterogeneous integration involves bonding materials such as III-V compounds onto silicon.

Bowers first worked on III-V bonding with HP to make longer wavelength - 1310nm and 1550nm - VCSELs. “We had been bonding indium phosphide and gallium arsenide to solve a fundamental problem that indium phosphide does not make good mirrors,” he says. “So I was pretty confident we could bond III-V to silicon to add gain to silicon photonics to then add all the laser capability.”

Bonding to silicon is attractive as it enables the integration of optical features that haven't been widely integrated onto any other platform, says Bowers. These include not only lasers but other active devices such as modulators and photo-detectors, as well as passive functions such as isolators and circulators.

One concern raised about heterogeneous integration and the use of III-V materials is the risk of contamination of a CMOS fabrication line.

Bowers points out that the approached used does not impact the front end of the fabrication, where silicon wafers are etched and waveguides formed. The III-V material is bonded to the wafer at the fab’s back end, the stage where metallisation occurs when making a CMOS chip.

The leading chipmakers are also experimenting with III-V materials to create faster digital devices due to their higher electron mobility. “This is part of the natural evolution of CMOS,” he says. It remains unclear if this will be adopted, but it is possible that a 5nm CMOS node will use indium phosphide.

“All the CMOS houses are doing lots of work on III-V and silicon,” says Bowers. “They have figured out how to control that contamination issue.”

New capabilities

Bowers and his team have already demonstrated the integration of new optical functions on silicon.

“Neither silicon nor indium phosphide has an isolator and one always has to use an external YIG (yttrium iron garnet) isolator to reduce the reflection sensitivity of things like widely tunable lasers,” says Bower.

His team has developed a way to bond a YIG onto silicon using the same techniques it uses for bonding III-V materials. The result is an integrated isolator device with 32dB isolation and a 2dB insertion loss, a level of performance matching those of discrete isolators.

Incorporating such functionality onto silicon creates new possibilities. “We have a paper coming out that features a 6-port circulator,” says Bowers. “It is not a tool that the community can use yet because it has never been made before but we can do that on silicon now,” he says. “That is a good new capability.”

Superior performance

Bowers stresses that heterogeneous integration can also result in optical performance superior to a III-V design alone. He cites as an example how using a silicon nitride waveguide, with its lower loss that indium phosphide or gallium arsenide, can create high-quality Q-resonators.

A Q-resonator can be viewed as a form of filter. Bowers' group have demonstrated one with a Q of 80 million. “That makes it very sensitive to a variety of things,” he says. One example is for sensors, using a Q resonator with a laser and detector to form a spectrometer.

His researchers have also integrated the Q resonator with a laser to make a widely tunable device that has a very narrow line-width: some 40kHz wide. This is a narrower than the line-width of commercially-available tunable lasers and exceeds what can be done with indium phosphide alone, he says.

Challenges

Bowers, like other silicon photonics luminaries, highlights the issues of automated packaging and automated testing, as important challenges facing silicon photonics. “Taking 10,000s of transceivers and bringing all the advanced technology - not just processing but test and packaging - that are being developed for cell phones,” he says.

Too much of photonics today is based on gold boxes and expensive transceivers. “Where Aurrion and Intel are going is getting silicon photonics to the point where photonics will be ubiquitous, cheap and high yielding,” he says. This trend is even evident with his university work. The 400-element 2.54-terabit network-on-a-chip has very high laser yields, as are its passive yields, he says.

“So, effectively, what silicon photonics can do is going up very rapidly,“ says Bowers. “If you can put it in the hands of a real CMOS player like Intel or the companies that Aurrion uses, it is going to take photonics to a whole new area that people would not have thought possible in terms of complexity.”

Yet Bowers is also pragmatic. “It still takes time,” he says. “You can demonstrate an idea, but it takes time to make it viable commercially.”

He points to the recently announced switch from Oracle that uses mid-board optics. “That is a commercial product out there now,” he says. “But is it silicon photonics? No, it is VCSEL-based; that is the battle going on now.”

VCSELs have won the initial battle in the data centre but the amount of integration the technology can support is limited. Once designers move to wavelength-division multiplexing to get to higher capacities, where planar technology is required to combine and separate the different wavelengths efficiently, that is when silicon has an advantage, he says.

The battle at 100 gigabit between VCSELs and silicon photonics is also one that Bowers believes silicon photonics will eventually win. But at 400 gigabit and one terabit, there is no way to do that using VCSELs, he says.

Status

The real win for silicon photonics is when optics moves from transceivers at the edge of the board to mid-board and eventually are integrated with a chip in the same package, he says.

Advanced chips such as switch silicon for the data centre are running into an input-output problem. There are only so many 25 gigabit-per-second signals a chip can support. Each signal, sent down a trace on a printed circuit board, typically requires equalisation circuitry at each end and that consumes power.

Most of the photonics industry has focused on telecom and datacom, and justifiably so. The next big thing will happen in the area of sensors.

A large IC packaged as a ball grid array may have as many as 5,000 bumps (balls) that are interfaced to the printed circuit board. Using photonics can boost the overall bandwidth coming on and off the chip.

“With photonics, and in particular when we integrate the laser as well as the modulator, the world doesn't see it as a photonics chip, it's an electronics chip, it just turns out that some of those bumps are optical ones and they provide much more efficient transmission of data and at much lower power,” say Bowers. A 100 terabit of even a 1000 terabit - a petabit - switch chip then becomes possible. This is not possible electrically but it is possible by integrating photonics inside the package or on the chip itself, he says.

“That is the big win eventually and that is where we help electronics extend Moore’s law,” says Bowers.

And as silicon photonics matures, other applications will emerge - More than Moore’s law - like the use of photonics for sensors.

“Most of the photonics industry has focused on telecom and datacom, and justifiably so,” says Bowers. “The next big thing will happen in the area of sensors.”

Professor Bowers was interviewed before the Juniper Networks announcement

Intel's 100-gigabit silicon photonics move

Intel has unveiled two 100-gigabit optical modules for the data centre made using silicon photonics technology.

The PSM4 and CWDM4/CLR4 100-gigabit modules mark the first commercial application of a hybrid integration technique for silicon photonics, dubbed heterogeneous integration, that Intel has been developing for years.

Intel's 100-gigabit module announcement follows the news that Juniper Networks has entered into an agreement to acquire start-up, Aurrion, for $165 million. Aurrion is another silicon photonics player developing this hybrid integration technology for its products.

Hybrid integration

With heterogeneous integration, materials such as indium phosphide and gallium arsenide can be bonded to the silicon substrate before the 300mm wafer is processed to produce the optical circuit. Not only can lasers be added to silicon but other active devices such as modulators and photo-detectors as well as passive functions such as isolators and circulators.

There is no alignment needed; we align the laser with lithography

Intel is using the technique to integrate the laser as part of the 100-gigabit transceiver designs.

"Once we apply the light-emitting material down to the silicon base wafer, we define the laser in silicon," says Alexis Bjorlin, vice president and general manager, Intel Connectivity Group. “There is no alignment needed; we align the laser with lithography.”

Intel claims it gets the highest coupling efficiency between the laser and the optical waveguide and modulator because it is lithographically defined and requires no further alignment.

100-gigabit modules

Intel is already delivering the 100-gigabit PSM4 module. “First volume shipments are happening now,” says Bjorlin. Microsoft is one Internet content provider that is using Intel’s PSM4.

The chip company is also sampling a 100-gigabit CWDM4 module that also meets the more demanding CLR4 Alliance’s optical specification. The 100-gigabit CLR4 module can be used without forward-error correction hardware and is favoured for applications where latency is an issue such as high-performance computing.

Intel is not the first vendor to offer PSM4 modules, nor is it the first to use silicon photonics for such modules. Luxtera and Lumentum are shipping silicon photonics-based PSM4 modules, while STMicroelectronics is already supplying its PSM4 optical engine chip.

We are right on the cusp of the real 100-gigabit connectivity deployments

“Other vendors have been shipping PSM4 modules for years, including large quantities at 40 gigabit,” says Dale Murray, principal analyst at LightCounting Market Research. “Luxtera has the clear lead in silicon photonics-based PSM4 modules but a number of others are shipping them based on conventional optics.”

The PSM4 is implemented using four independent 25-gigabit channels sent over a single-mode ribbon fibre. Four fibres are used for transmission and four fibres for receive.

“The PSM4 configuration is an interesting design that allows one laser to be shared among four separate output fibres,” says Murray. “As Luxtera has shown, it is an effective and efficient way to make use of silicon photonics technology.”

The CWDM4 is also a 4x25-gigabit design but uses wavelength-division multiplexing and hence a single-mode fibre pair. The CWDM4 is a more complex design in that an optical multiplexer and demultiplexer are required and the four lasers operate at different wavelengths.

“While the PSM4 module does not break new ground, Intel’s implementation of WDM via silicon photonics in a CWDM4/CLR4 module could be more interesting in a low-cost QSFP28 module,” says Murray. WDM-based QSFP28 modules are shipping from a number of suppliers that are using conventional optics, he says.

Intel is yet to detail when it will start shipping the CWDM4/CLR4 module.

Market demand

Bjorlin says the PSM4 and the CWDM4/CLR4 will play a role in the data centre. There are applications where being able to break out 100-gigabit into 25-gigabit signals as offered by the PSM4 is useful, while other data centre operators prefer a duplex design due to the efficient use of fibre.

“We are right on the cusp of the real 100-gigabit connectivity deployments,” she says.

As for demand, Bjorlin expects equal demand for the two module types in the early phases: “Longer term, we will probably see more demand for the duplex solution”.

LightCounting says that 100-gigabit PSM4 modules took an early lead in the rollout of 100 Gigabit Ethernet, with VCSEL-based modules not far behind.

“Some are shipping CWDM4/CLR4 and we expect that market to ramp,” says Murray. “Microsoft and Amazon Web Services seem to like PSM4 modules while others want to stick with modules that can use duplex fibre.

Source: Intel

Source: Intel

Data centre switching

“One of the most compelling reasons to drive silicon photonics in the future is that it is an integratable platform,” says Bjorlin.

Switch silicon from the likes of Broadcom support 3.2 terabits of capacity but this will increase to 6.4 terabits by next year and 12.8 terabits using 4-level pulse amplitude modulation (PAM-4) signalling by 2018 (see chart). And by 2020, 25.6-terabit capacity switch chips are expected.

The demand for 100 gigabit is for pluggable modules that fit into the front panels of data center switches. But the market is evolving to 400-gigabit embedded optics that sit on the line card, she says, to enable these emerging higher-capacity switches. Intel is a member of the Consortium of On-Board Optics (COBO) initiative that is being led by Microsoft.

“When you get to 25.6-terabit switches, you start to have a real problem getting the electrical signals in and out of the switch chip,” says Bjorlin. This is where silicon photonics can play a role in the future by co-packaging the optics alongside the switch silicon.

“There will be a need for an integrated solution that affords the best power consumption, the best bandwidth-density that we can get and effectively position silicon photonics for optical I/O [input/output],” says Bjorlin. “Ultimately, that co-packaging is inevitable.”

Juniper Networks to acquire Aurrion for $165 million

The announcement of the acquisition was low key. A CTO blog post and a statement that Juniper Networks had entered into an agreement to acquire Aurrion, the fabless silicon photonics start-up. No fee was mentioned.

However, in the company's US Securities and Exchange Commission filing, Juniper values the deal at approximately $165 million. "The Company believes the acquisition will help to fuel its long-term competitive advantage by enabling cost-effective, high-density, high-speed optical networks," it said. The deal is expected to be closed this quarter.

Ciena acquired Teraxion, while in recent years Cisco acquired Lightwire, Mellanox bought Kotura and Huawei bought a small Belgium start-up, Caliopa. Meanwhile, other vendors have their own silicon photonics developments. Intel is one, Nokia has Bell Labs while Coriant has its own silicon photonics R&D.

But the deal is significant for a number of reasons.

First, Aurrion, like Intel, is a proponent of heterogeneous integration, combining indium phosphide and other technologies on a silicon wafer platform through bonding. The approach has still to be proven in commercial volumes but it promises the use of III-V materials on 12-inch silicon wafers manufactured in a chip fabrication plant.

Aurrion has made tunable lasers for telecom that cover both the C- and L-bands, as well as uncooled laser arrays for datacom applications. The start-up has also been developing high-speed transceivers for the data centre.

The company has also been working on the manufacturing aspects of silicon photonics, a considerable undertaking. These include automated wafer-scale testing, connecting fibre to a silicon photonics chip, and packaging.

Juniper is thus getting an advanced silicon photonics technology suited for volume manufacturing that it will use to advance its data centre networking offerings.

Juniper may choose to make its own optical transceivers but, more likely, it will use silicon photonics as part of its switch designs to tackle issues of data centre scaling and the continual challenge of growing power consumption. It could also use the technology for its IP core routers and longer term, to tackle I/O issues alongside custom ASICs.

Systems vendors drive silicon photonics

The Aurrion acquisition also highlights how it is systems vendors that are acquiring silicon photonics start-ups rather than the traditional optical component and module makers.

This is partly a recognition that silicon photonics' main promise is as a systems technology. Acacia, the coherent transmission specialist, is one company that has shown how silicon photonics can benefit optical module design but the technology's longer-term promise is for systems design rather than optical modules.

A consequence of such acquisitions by systems vendors is that technology being developed by silicon-photonics start-ups is being swallowed within systems houses for their own use and not for the merchant market. Systems vendors have deep pockets to develop the technology but it will be for their own use. For the wider community, silicon photonics technology being developed by the likes of Aurrion is no longer available.

This is what AIM Photonics, the US public-private partnership that is developing technology for integrated photonics, is looking to address: to advance the manufacturing of silicon photonics, making the resulting technology available to small to medium sized businesses and entrepreneurial ventures. However, AIM Photonics is one year into a five-year venture.

Implications

Should major systems vendors owning silicon photonics technology in-house concern the traditional optical component vendors?

Not for now.

Optical transceiver sales continue to grow and the bulk of designs are not integrated. And while silicon photonics is starting to be used for integrated designs, it is competing against the established technologies of indium phosphide and gallium arsenide.

But as photonics moves closer to the silicon and away from a system's faceplate, silicon photonics becomes more strategically important and this is where systems vendors can start developing custom designs.

Must the systems houses own the technology to do that?

Not necessarily, but they will need silicon photonics design expertise, and in the case of Juniper, it can hit the ground running with Aurrion.

Longer term, it will be the much larger chip industry that will drive silicon photonics rather than the optical industry. There are chip foundries now that are making silicon photonic ICs as there are top-ten chip companies such as Intel and STMicroelectronics. But ultimately it will be a very different supply chain that will take shape.

It is early days but Juniper's acquisition is the latest indicator that it is the systems vendors that are moving first at the very beginnings of this new ecosystem.

X-Celeprint brings printing technology to silicon photonics

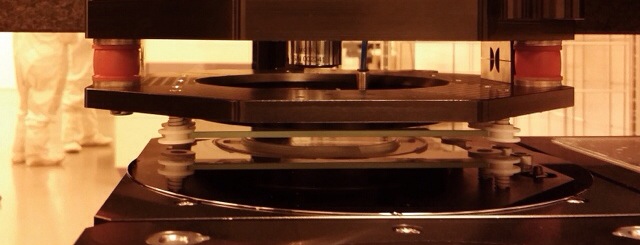

X-Celeprint's micro transfer printing technology. Source: X-Celeprint

X-Celeprint's micro transfer printing technology. Source: X-Celeprint

- X-Celeprint has a printing process that places individual 'chiplets' of III-V material onto silicon

- The micro transfer printing technique can be used to make silicon photonics circuits

- X-Celeprint will work with silicon photonics companies interested in licensing its technology

A key challenge facing silicon photonics players is creating a light source. Silicon does not lase so a III-V material is needed to form the laser.

One approach is to attach a tiny module holding the laser to the silicon photonics design. This is what the likes of Cisco Systems, Luxtera, Mellanox Technologies and IBM are doing: adding an external laser to the otherwise monolithic silicon photonics circuit.

An alternative technique is to bond the III-V material to the silicon and using photolithography and etching to construct the silicon photonics device. The attraction of III-V bonding is that the technique can be used to also make the modulators and photo-detectors. Known as heterogeneous integration, this approach is being used by companies such as Aurrion, Intel and Skorpios Technologies.

"Bonding is an elegant solution," says Roel Baets, a professor at the Photonics Research Group at Ghent University. "You can make the light source at the wafer scale and have a single chip solution that looks like a monolithic chip, including the light source."

Think of printing as pick-and-place in a massively parallel fashion. Instead of ink, we are picking up and printing arrays of high-performance semiconductors.

Bonding III-V material to silicon is itself non-trivial. First, silicon wafers are either 200mm or 300mm (8 or 12 inch) while III-V indium phosphide wafers are typically 50mm (2 inch). Indium phosphide wafers are also expensive, simply etching away the majority of the wafer to leave small islands of wanted material is hugely wasteful.

"There is only going to be a laser here or there, with a fill factor - an area coverage - of some one percent," says Baets. "You are throwing away a lot of III-V."

Equally, cutting up the III-V wafer into small slivers for bonding is complicated as it requires precision placement; a process difficult to automate to achieve high-yield circuits. This is the challenge the heterogeneous integration companies have set themselves.

It is a market opportunity identified by start-up X-Celeprint. It has a process that places individual 'chiplets' of III-V material onto silicon by the thousands.

X-Celeprint uses a micro transfer printing to place the chiplets onto silicon. "Think of printing as pick-and-place in a massively parallel fashion," says Kyle Benkendorfer, CEO of X-Celeprint. "Instead of ink, we are picking up and printing arrays of high-performance semiconductors."

Micro transfer printing is already used commercially to make high concentration solar cells, and it is being evaluated to place thin lasers on read/ write heads in disc drives. "We can print live devices or a slab of material on any substrate as long as it is flat," says Benkendorfer.

One benefit of the technique is that the thin III-V material is removed from the indium phosphide wafer but the underlying substrate is retained and can be recycled. For wafer-to-wafer bonding, in contrast, the substrate must be ground back. "This is several hundred microns of [substrate] material," says Benkendorfer. "With our process you can reprocess the wafer and regrow it, saving some $3,000."

The printing process also lends itself to automation. "We can very efficiently place active die of highly expensive compound material at the point of use, where it can then be converted into a device," he says.

X-Celeprint wants to work with silicon photonics companies interested in licensing its printing technology. Developing the process with a particular silicon photonics vendor takes time. Each application requires tailoring and it can take up to two years to make, test and scale up production, says the start-up.

"We recognise that silicon photonics as a large market is out there, no question," says Benkendorfer. "But the development time to get any significant market is going to be a while."

Is silicon photonics an industry game-changer?

Briefing: Silicon Photonics

Part 3: Merits, challenges and applications

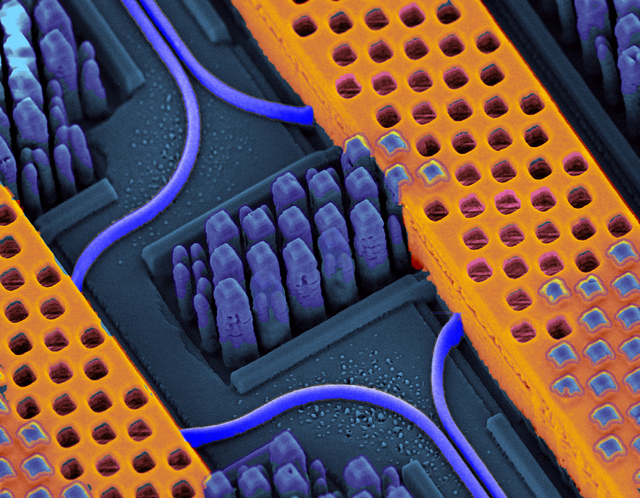

Shown in blue are the optical waveguides (and bend radius) while the copper wires carrying high-speed electrical signals are shown in orange. Source: IBM

Shown in blue are the optical waveguides (and bend radius) while the copper wires carrying high-speed electrical signals are shown in orange. Source: IBM

System vendors have been on a silicon-photonics spending spree.

Cisco Systems started the ball rolling in 2012 when it acquired silicon photonics start-up, LightWire, for $272M. Mellanox Technologies more recently bought Kotura for $82M. Now Huawei has acquired Caliopa, a four-year-old Belgium-based start-up, for an undisclosed fee. The Chinese system vendor has said it is looking to further bolster its European R&D, and highlighted silicon photonics in particular.

Given that it was only just over a decade ago when systems companies were shedding their optical component units, the trend to acquire silicon photonics highlights the growing importance of the fledgling technology.

These system vendors view silicon photonics as a strategic technology. The equipment makers want to develop expertise and experience as they plan to incorporate the technology in upcoming, hopefully differentiated platforms.

"If I have a Terabit of capacity on the front panel, how am I going to manipulate that across the line card, a fabric or the backplane?" says Adam Carter, general manager and senior director of the transceiver modules group at Cisco Systems. "We saw silicon photonics as a technology that could potentially enable us to get there."

System vendors are already using embedded optics - mounted on boards close to the ICs instead of pluggable modules on the front panel - to create platforms with denser interfaces.

"Photonics doesn't need the latest and greatest lithography"

Arista Networks' 7500E switch has a line card with board-mounted optics rather than pluggable transceivers to increase 100 Gigabit port density. The company offers several line cards using pluggable modules but it has designed one card with board-mounted optics that offers flexible interfaces - 10 Gig, 40 Gig and 100 Gig - and a higher port density. When developing the design, the multi-source agreement (MSA) CFP2 pluggable module was not ready, says Arista.

Compass-EOS, a core IP router start-up, has developed chip-mounted optics based on 168 lasers and 168 detectors. The novel Terabit-plus optical interface removes the need for a switch fabric and the mid-plane to interconnect the router card within the platform. The interface also enables linking of platforms to scale the IP core router.

Both companies are using VCSELs, an established laser technology that silicon photonics competes with. Yet the two designs highlight how moving optics closer to chips enables system innovation, a development that plays to silicon photonics' strength.

"I characterise silicon photonics as a technology that will compete in the right applications but won’t displace indium phosphide" Ed Murphy, JDSU

Silicon photonics promises cost savings by enabling vendors to piggyback on the huge investments made by the semiconductor industry. Vendors making their own products, such as optical transceivers, also promises to shake up the existing optical component supply chain.

Cisco Systems' first silicon photonics product is the proprietary 100 Gigabit optical CPAK transceiver that is undergoing qualification. By making its own optical module, Cisco avoids paying the optical module makers' margins. Cisco claims the CPAK's smaller size improves the faceplate density compared to the CFP2.

Pros and cons

Silicon photonics may be able to exploit the huge investment already made in the semiconductor industry, but it does differ from standard CMOS integrated circuits (ICs).

First, optics does not have the equivalent of Moore's Law. Whereas chip economics improve with greater integration, only a few optical functions can be cascaded due to the accumulated signal loss as light travels through the photonic circuit. This is true for optical integration in general, not just silicon photonics.

Another issue is that the size of an optical component - a laser or a modulator - is dictated by the laws of physics rather than lithography. "Photonics doesn't need the latest and greatest lithography," says Martin Zirngibl, domain leader for enabling physical technologies at Alcatel-Lucent's Bell Labs. "You can live with 100nm, 120nm [CMOS] components whereas for electronics you want to have 45nm."

This can lead to the interesting situation when integrating electronics with photonics. "You either don't use the latest technology for electronics or you waste a lot of real estate with very expensive lithography for photonics," says Zirngibl.

Another disadvantage of silicon is that the material does not lase. As a result, either a III-V material needs to be bonded to the silicon wafer or an external laser must be coupled to the silicon photonics circuit.

Silicon also has relatively small waveguides which make it tricky to couple light in and out of a chip.

The advantages of silicon photonics, however, are significant.

The technology benefits from advanced 8- and 12-inch wafers and mature manufacturing processes developed by the semiconductor industry. Using such CMOS processes promises high yields, manufacturing scale, and automation and testing associated with large scale IC manufacturing.

"This is probably the only advantage but it is very significant," says Valery Tolstikhin, founder and former CTO of indium phosphide specialist, OneChip Photonics, and now an independent consultant. "It takes silicon totally off the scale compared to any other photonics materials."

"We can build the single-die optical engine in the same CMOS line where processors are built, where billions [of dollars] of investment has been done"

IBM's high-density silicon photonics optical engine is made using a 90nm CMOS process. "We can build the single-die optical engine in the same CMOS line where processors are built, where billions [of dollars] of investment has been done," says Yurii Vlasov, manager of the silicon nanophotonics department at IBM Research. "We are riding on top of that investment."

Extra processing may be introduced for the photonics, says IBM, but the point is that there is no additional capital investment. "It is the same tooling, the same process conditions; we are changing the way this tooling is used," says Vlasov. "We are changing the process a little bit; the capital investment is in place."

"We believe that even for shorter distance, silicon photonics does compete in terms of cost with VCSELs." Yurii Vlasov, IBM

Stephen Krasulick, CEO of silicon photonics start-up, Skorpios Technologies, makes a similar point. "The real magic with our approach is the ability to integrate it with standard, commercial fabs," he says.

Skorpios is a proponent of heterogeneous integration, or what the company refers to as 'silicon photonics 2.0'. Here silicon and III-V are wafer-bonded and the optical components are created by etching the two materials. This avoids the need to couple external lasers and to use active alignment.

"We do it in a manner such that the CMOS foundry is comfortable letting the wafer back into the CMOS line," says Krasulick, who adds that Skorpios has been working with CMOS partners from the start to ensure that its approach suits their manufacturing flow.

Applications

The first applications adopting silicon photonics span datacom and telecom: from short-reach interconnect in the data centre to 100 Gigabit-per-second (Gbps) long-distance coherent transmission.

Intel is developing silicon photonics technology to help spur sales of its microprocessors. The chip giant is a member of Facebook's Open Compute Project based on a disaggregated system design that separates storage, computing and networking. "When I upgrade the microprocessors on the motherboard, I don't have to throw away the NICs [network interface controllers] and disc drives," says Victor Krutul, director business development and marketing for silicon photonics at Intel. The disaggregation can be within a rack or span rows of equipment.

"Optical modules do not require state-of-the-art lithography or large scale photonic integration, but they do need to be coupled in and out of fibre and they need lasers - none of that silicon photonics has a good solution for"

Intel has developed the Rack Scale Architecture (RSA) which implements a disaggregated design. One RSA implementation for Facebook uses three 100Gbps silicon photonics modules per tray. Each module comprises four transmit and four receive fibres, each at 25Gbps. Each tray uses a Corning-developed MXC connector and its ClearCurve fibre that support data rates up to 1.6Tbps. “Different versions of RSA will have more or less modules depending on requirements," says Krutul.

Luxtera, whose silicon photonics technology has been used for active optical cables, and Mellanox's Kotura, are each developing 100Gbps silicon photonics-based QSFPs to increase data centre reach and equipment face plate density.

One data centre requirement is the need for longer reach links. VCSEL technology is an established solution but at 100Gbps its reach is limited to 100m only. Intel's 100Gbps module, operating at 1310nm and combined with Corning's MXC connector and ClearCurve multi-mode fibre, enables up to 300m links. But for greater distances - 500m to 2,000m - a second technology is required. Data centre managers would like one technology that spans the data centre yet is cost competitive with VCSELs.

"Silicon photonics lends itself to that," says Cisco's Carter. "If we drive the cost lower, can we start looking at replacing or future proofing your network by going to single mode fibre?"

"There are places where silicon photonics will definitely win, such as chip-to-chip optical interconnects, and there are places where there is still a question mark, like fibre-optics interconnects." Valery Tolstikhin

IBM's 25Gbps-per-channel optical engine has been designed for use within data centre equipment. "We are claiming we have density based on optical scaling which is the highest in the industry, and we have done it using monolithic integration: optical devices are built side-by-side with CMOS," says Vlasov.

What is important, says Vlasov, is not so much the size of the silicon waveguide but how sharp its bend radius is. The bend radius dictates how sharply the light can be guided while remaining confined within the integrated circuit. The higher the light confinement, the smaller the bend radius and hence the overall circuit area.

Much progress has been made in improving light confinement over the past two decades, resulting in the bend ratio coming down from 1cm to a micron. IBM claims that with its technology, it can build systems comprising hundreds of devices occupying a millimeter. "That is a major difference in the density of optical integration," says Vlasov.

IBM does not use heterogeneous integration but couples lasers externally."It is not complicated, it is a technical problem we are solving; we believe that is the way to go," says Vlasov. "The reason why we have gone down this path is very simple: we believe in monolithic integration where electrical circuitry sits side by side with optical components."

Such monolithic integration of the optics with the electronics, such as modulator drivers and clock recovery circuitry, reduces significantly the cost of packaging and testing. "We believe that even for shorter distances, silicon photonics does compete in terms of cost with VCSELs if all elements of the cost are taken care of: bill of materials, packaging and testing," says Vlasov.

But not everyone believes silicon photonics will replace VCSELs.

For example, Tolstikhin questions the merits of silicon photonics for transceiver designs, such as for 100 Gig modules in the data centre. "There are places where silicon photonics will definitely win, such as chip-to-chip optical interconnects, and there are places where there is still a question mark, like fibre-optics interconnects," he says.

Tolstikhin argues that silicon photonics offers little advantage for such applications: "Optical modules do not require state-of-the-art lithography or large scale photonic integration, but they do need to be coupled in and out of fibre and they need lasers - none of that silicon photonics has a good solution for."

Cisco says it was first attracted to LightWire's technology because of its suitability for optical transceivers. Six years ago 1W, SFP+ modules were limited to 10km. "Customers wanted 40km, 80km, even WDM," says Carter. "They [LightWire] did a 40km SFP+ using their modulator that consumed only 0.5W - a huge differentiator." Two years ago 100 Gig CFP modules were at 24W while LightWire demonstrated a module under 8W, says Carter.

Tolstikhin believes silicon photonics' great promise is for applications still to emerge. One example is chip-to-chip communication that has modest optical light requirements and does not have to be coupled in and out of fibre.

"Here you have very high requirements for density packaging and the tiny [silicon] waveguides are handy whereas indium phosphide is too big and too expensive here," says Tolstikhin. Longer term still, silicon photonics will be used for on-chip communication but that will likely be based on deep sub-wavelength scale optics such as surface plasmonics rather than classical dielectric waveguides.

Tolstikhin also argues that the economics of using indium phosphide compared to silicon photonics need not be all that gloomy.

Indium phosphide is associated with custom small-scale fabs and small volume markets. But indium phosphide can benefit from the economics of larger industries just as silicon photonics promises to do with the semiconductor industry.

Indium phosphide is used in higher volume for wireless ICs such as power amplifiers. "Quite significantly orders of magnitude higher," says Tolstikhin. The issue is that, conventionally, photonic circuits are fabricated by using multiple epitaxial growth steps, whereas the wireless ICs are made in a single-growth process, hence epitaxy and wafer processing are decoupled.

"If you can give up on regrowth and still preserve the desired photonic functionality, then you can go to commercial RF IC fabs," he says. "This is a huge change in the economic model." It is an approach that enables a fabless model for indium phosphide photonics, with the potential advantages not unlike those claimed by silicon photonics with respect to commercial CMOS fabs.

"That suggests indium phosphide - which has all kinds of physical advantages for those applications that require transmitters, receivers and fibre, plus readily available high-speed analogue electronics for trans-impedance amplifiers and laser or modulator drivers - may be quite a competitive contender," says Tolstikhin.

"Silicon photonics has a certain capability but the hype around it has magnified that capability beyond reality"

Customers don't care which technology is used inside a transceiver. "They care only about cost, power and package density," says Tolstikhin. "Indium phosphide can be competitive and on many occasions beat silicon photonics."

JDSU also believes that long-term, a perfect fit for silicon photonics may be relative short reach interconnects – chip-to-chip and board-to-board reaches. “You need to have very high speed and dense interconnects, I can see that as being a very strong value proposition long term," says Ed Murphy, senior director, communications and commercial optical products at JDSU.

Finisar and JDSU are open to the potential benefits of silicon photonics but remain strong proponents of traditional optical materials such as indium phosphide and gallium arsenide.

"We have designed silicon photonic chips here at Finisar and have evaluations that are ongoing. There are many companies that now offer silicon photonics foundry services. You can lay out a chip and they will build it for you," says Jerry Rawls, executive director of Finisar. "The problem is we haven't found a place where it can be as efficient or offer the performance as using traditional lasers and free-space optics."

"Silicon photonics has a certain capability but the hype around it has magnified that capability beyond reality,” says JDSU's Murphy. "Practitioners of silicon photonics would tell you that as well."

According to Murphy, each application, when looked at in detail, has its advantages and disadvantages when using either silicon photonics or indium phosphide. “Even in those applications where one or the other is better, the level of improvement is measured in a few tens of percent, not factors of ten,” he says. "I characterise silicon photonics as a technology that will compete in the right applications but won’t displace indium phosphide."

Silicon photonics for telecom

At the other extreme of the optical performance spectrum, silicon photonics is being developed for long-distance optical transmission. The technology promises to help shrink coherent designs to fit within the CFP2 module, albeit at the expense of reach. A CFP2 coherent module has extremely challenging cost, size and power requirements.

Teraxion is developing a coherent receiver for CFP2. "We believe silicon photonics is the material of choice to fulfill CFP2 requirements while allowing even smaller size reduction for future modules such as the CFP4," said Martin Guy, Teraxion's vice president of product management and technology.

u2t Photonics and Finisar recently licensed indium phosphide modulator technology to help shrink coherent designs into smaller form factor pluggables. So what benefit does silicon photonics offer here?

"In terms of size there will not be much difference between indium phosphide and silicon photonics technology," says Guy. "However, being on each side on the fence, we know that process repeatability and therefore yield is better with silicon photonics." Silicon photonics thus promises a lower chip cost.

"We have projects spanning everything from access all the way to long haul, and covering some datacom as well," says Rob Stone, vice president of marketing and program management at Skorpios. The start-up has developed a CMOS-based tunable laser with a narrow line width that is suitable for coherent applications.

"If you develop a library of macrocells, you can apply them to do different applications in a straightforward manner, provided all the individual macrocells are validated," says Stone. This is different to the traditional design approach.

Adding a local oscillator to a coherent receiver requires a redesign and a new gold box. "What we've got, we can plug things together, lay it out differently and put it on a mask," says Stone. "This enables us to do a lot of tailoring of designs really quite quickly - and a quick time-to-market is important."

Perhaps the real change silicon photonics brings is a disruption of the supply chain, says Zirngibl.

An optical component maker typically sells its device to a packaging company that puts it in a transmitter or receiver optical sub-assembly (TOSA/ ROSA). In turn, the sub-assemblies are sold to a module company which then sells the optical transceiver to an equipment vendor. Each player in the supply chain adds its own profit.

Silicon photonics promises to break the model. A system company can design its own chip using design tools and libraries and go to a silicon foundry. It could then go to a packaging company to make the module or package the device directly on a card, bypassing the module maker altogether.

Yet the ASIC model can also benefit module makers.

IBM has developed its 25Gbps-per-channel silicon photonics technology for its platforms, for chip-to-chip and backplanes, less for data centre interconnect. But it is open to selling the engine to interested optical module players. "If this technology can be extended to 2km for big data centres, others can come in, the usual providers of transceivers," says Vlasov.

"There are companies with the potential to offer a [silicon photonics] design service or foundry service to others that would like to access this technology," says Cisco's Carter. "Five years ago there wasn't such an ecosystem but it is developing very fast."

The article is an extended version of one that appeared in the exhibition magazine published at ECOC 2013.

Part 1: Optical interconnect, click here

Part 2: Bell Labs on silicon photonics, click here

Aurrion mixes datacom and telecom lasers on a wafer

"There is an inevitability of the co-mingling of electronics and optics and we are just at the beginning"

"There is an inevitability of the co-mingling of electronics and optics and we are just at the beginning"

Eric Hall, Aurrion

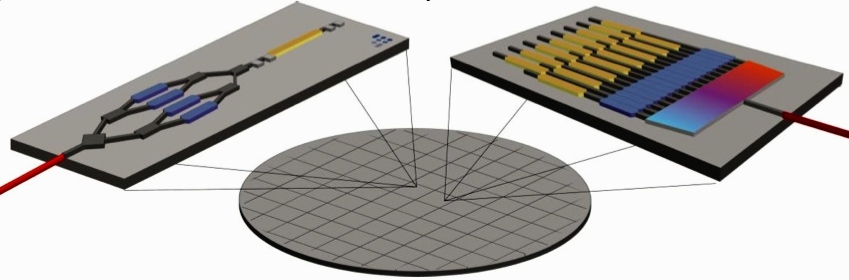

Aurrion's long-term vision for its heterogeneous integration approach to silicon photonics is to tackle all stages of a communication link: the high-bandwidth transmitter, switch and receiver. Heterogeneous integration refers to the introduction of III-V material - used for lasers, modulators and receivers - onto the silicon wafer where it is processed alongside the silicon using masks and lithography.

In a post-deadline paper given at OFC/NFOEC 2013, the fabless start-up detailed the making of various transmitters on a silicon wafer. These include tunable lasers for telecom that cover the C- and L-bands, and uncooled laser arrays for datacom.

The lasers are narrow-linewidth tunable devices for long-haul coherent applications. According to Aurrion, achieving a narrow-linewidth laser typically requires an external cavity whose size makes it difficult to produce a compact design when integrated with the modulator.

Having a tunable laser integrated with the modulator on the same silicon photonics platform will enable compact 100 Gigabit coherent pluggable modules. "The 100 Gig equivalent of the tunable XFP or SFP+," says Eric Hall, vice president of business development at Aurrion.

Hall admits that traditional indium-phosphide laser manufacturers will likely integrate tunable lasers with the modulator to produce compact narrow-linewidth designs. "There will be other approaches but it is exciting that we can now make this laser and modulator on this platform," says Hall. "And it becomes very exciting when you make these on the same wafer as high-volume datacom components."

Aurrion's vision of a coherent transmitter and a 16-laser array made on the same wafer. Source: Aurrion

Aurrion's vision of a coherent transmitter and a 16-laser array made on the same wafer. Source: Aurrion

The wafer's datacom devices include a 4-channel laser array for 100GBASE-LR4 10km reach applications and a 400 Gigabit transmitter design comprising 2x8 wavelength division multiplexing (WDM) arrays for a 16x25Gbps design, each laser spaced 200GHz apart. These could be for 10km or 40km applications depending on the modulator used. "These arrays are for uncooled applications," says Hall. "The idea is these don't have to be coarse WDM but tighter-spaced WDM that hold their wavelength across 20-80oC."

Coarse WDM-based laser arrays do not require a thermo-electric cooler (TEC) but the larger spacing of the wavelengths makes it harder to design beyond 100 Gigabit, says Hall: "Being able to pack in a bunch of wavelengths yet not need a TEC opens up a lot of applications."

Such lasers coupled with different modulators could also benefit 100 Gigabit shorter-reach interfaces currently being discussed in the IEEE, including the possibility of multi-level modulation schemes, says the company.

Aurrion says it is seeing the trend of photonics moving closer to the electronics due to emerging applications.

"Electronics never really noticed photonics because it was so far away and suddenly photonics has encroached into its personal space," says Hall. "There is an inevitability of the co-mingling of electronics and optics and we are just at the beginning."

Q&A with Kotura's CTO: Integration styles and I/O limits

The second, and final part, of the Q&A with Mehdi Asghari, CTO of silicon photonics start-up, Kotura.

Part 2 of 2

"When do the big players adopt a new technology and go from an electrical to an optical solution? In my experience, usually when they absolutely have to."

Mehdi Asghari, CTO, Kotura

Q: Silicon photonics comes in two integration flavours: the monolithic approach where the modulators and detectors are implemented monolithically while the lasers are coupled externally (e.g. Kotura and Luxtera); and heterogeneous integration where III-V materials such as indium phosphide are bonded to the silicon to form a hybrid design yet are grown on a single die (e.g. Aurrion). Does one approach have an advantage?

A: I have a III-V background and converted to silicon photonics over 15 years ago. The key issue here is what are you trying to do? Why are we going from III-V processing to silicon? Is it the yield and process maturity or the device performance for actives?

If it is the former, then heterogeneous integration does not really solve the problem since you are still processing III-V devices and are likely to need multiple fabs to do it. If it is the latter then you should stick to III-V wafers.

The fact is that silicon provides passive performance that is far superior to III-V while the active performance – the detector and modulator - is good enough. In fact our germanium detectors could be better and our electro-absorption modulators can be lower power and exhibit a broader working spectral range.

We have seen repeatedly that being good enough is all that silicon has to show it can do to win and that it is certainly doing.

"It is not enough to offer a 10%, 20% or even a 50% cost saving when you are offering the customer a brand new solution that comes with all the risks and unknowns associated with that technology."

Kotura has developed components for telecom (variable optical attenuators, and the functions needed for a 100 Gig coherent receiver) yet its focus is on datacom. Why is that?

We started in telecom as we looked for low hanging fruit that could give us a good margin and an easy start in our early days. This is important for a start-up with a new technology. The well-entrenched incumbent technologies are hard to displace.

You have to find an application with a clear value proposition to get started. Once you have established yourself, your supply chain and manufacturing infrastructure, you can take on more challenging and larger market opportunities.

We see certain areas in datacom that are not well served by either the short reach optics or the telecom grade solutions. Extended reach data centre is one key area where short-reach optics based on VCSELs cannot cover the reach needed and conventional telecom solutions are inherently over-engineered and do not meet the power, cost and size needed.

We think silicon photonics can play a key role here as a starting point in datacom. A key advantage of our platform here is that we can do WDM [wavelength division multiplexing] and hence offer 100 Gig on a single fibre (per direction). This is a major cost saving for longer reaches (>>50m) deployed in such links.

There are some big system players with silicon photonics (Cisco Systems, Alcatel-Lucent) and several small merchant silicon photonics players, such as the companies mentioned in the previous question, which must develop products to sell while funding the development of their technologies. How do you expect the silicon photonics marketplace to evolve, especially now that the technology is being more widely embraced?

For silicon photonics to succeed commercially, we need a multitude of vibrant and successful players in the field. Some of these can be start-ups that lead the innovation in technology and manufacturing but others can be larger organisations that have invested to service an internal need or leverage an existing dominance in the market.

There is room and a necessity for both. It takes a village to raise a child. One single company will not turn silicon photonics into a successful commercial reality.

Cisco Systems has been talking about its proprietary CPAK transceiver. Here is an example of a system vendor using in-house silicon photonics for its own use. Why do you think about such a development? And is Kotura being approached by equipment vendors that want to work with you to develop a custom design?

It is not new for a large company like Cisco to try and make sure that is has its own proprietary components to go into its systems to protect their product and their margins. We see that in all industries.

In terms of other companies coming up with their own proprietary solutions, we do see more and more of this - and a lot more this year than last year - especially when you come off the telecom bandwagon and into the datacom environment: data centres and high-performance computing.

That is because the customer is in charge of the entire environment, the two ends of the link, they can leverage more value from the solution you have to offer without worrying about standards. This is one way for systems companies to leverage value from components.

People are starting to see that the conventional technologies they have deployed are hitting a wall. When they are deploying a new solution they are rethinking their hardware strategy, and how they leverage it to add more value and differentiation to their system.

New ways to architect systems are becoming possible. If you are able to avoid limitations such as distance between the processor and memory, the router and switches and so on, you can come up with a very different architecture for your system and solution.

When do the big players adopt a new technology and go from an electrical to an optical solution? In my experience, usually when they absolutely have to. Most people don't adopt a new solution until they really, really need to; when the value proposition completely outweighs the risk.

It is not enough to offer a 10%, 20% or even a 50% cost saving when you are offering the customer a brand new solution that comes with all the risks and unknowns associated with that technology.

You have to offer them something new, to enable a new application, to add value by enabling a feature, something they can leverage in their product.

When you say systems people adopt new technology when they hit a wall, can you highlight examples of these hurdles?

When you look at the adoption of optics coming from the copper-dominated connectivity, it is very interesting.

Originally, for optics to work its way into the copper world, it had to hide itself and look like a copper solution. People had no idea how to create connectors and they were worried about fibre. So it was disguised as a copper solution.

As customers have got used to it, we can now come out and be more open. We can now do more innovative things with optical transceivers. If you look at the adoption rate, it is being accelerated by customers' demand such as 25 Gigabit signalling.

We can see that the processors and the ASICs - a switch from Broadcom or a processor from Intel or AMD - they are running into I/O [input/ output] density bottlenecks. The chip area is pretty constant, the packages are about the standard size, the number of pins are going beyond what they can support, they have to ramp up the pin rate to about 25 Gigabit-per-second (Gbps), while there are also some 10Gbps pins.

But the number of 25Gbps pins are becoming so high, potentially many hundreds, that they are not going to be able to trace them into the PCB (printed circuit board). The PCB can only take a 25Gbps signal for about 4 inches (~10cm) and then you need serdes [serialiser/ deserialiser) and repeaters.

You may imagine a current router or switch ASIC having ten 25Gbps pins and 100 10Gbps pins. The 10Gbps pins I can take to the edge and use 10Gbps transceivers; and the ten 25Gbps pins I can still do something about it. I may need a lot of electronics and serdes, and use pre-emphasis and equalisation.

But the next generation, when it becomes 100 25Gbps pins, you just cannot do that at the board level. That is where we will start to have to use optics close to the chip.

Will they go for very compact transceivers that sit next to the ASIC or would they try and co-package it with the ASIC?

My perception is that the first generation will be next to the ASIC. People will not integrate an unknown technology into a multi-billion dollar business, they will hedge their bets and have an external solution that offers them some level of assurance that if one solution does not work, they can change to another. But once they get used to it, they can start to integrate these in a multi-chip module solution.

What are the timescales?

I see transceivers next to the ASICs being deployed around 2017-18, maybe a bit sooner, with the co-packaging around 2018-20. People are already talking about it but usually these things take longer.

For part 1 of the Q&A, click here

Further reading: