Compass-EOS raises $42M

Compass-EOS has raised $42 million in investment. The Israeli start-up launched its r10004 IP core router in March and has so far announced two customers: NTT Communications and the China Education and Research Network, CERNET. The company says it has a second, tier-one operator that has yet to be announced.

Asaf Somekh with the icPhotonics chip

Asaf Somekh with the icPhotonics chip

"Both global operators have purchased routers on several occasions for several types of deployments," says Asaf Somekh, vice president of marketing at Compass-EOS. “There are also a couple of smaller operators that we cannot disclose at this stage." The company is involved in several trials in the US, Japan and EMEA.

The r10004 core router uses the company's novel icPhotonics chip that has a Terabit-plus optical interface. The chip, which houses a merchant network processor, integrates 168, 8 Gigabit VCSELs and 168 photodetectors for a total bandwidth of 1.344Tbps in each direction.

Eight chips are connected in a full mesh, removing the need for a router's switch fabric and mid-plane that connect the router cards. The result is a 6U-sized compact router platform that saves on power and cost.

First router deployments have been operational for over a year. Somekh says customers have been positive about the router's ease of deployment, operation and robustness, and have not encountered significant issues with deployments. "This is very different from their past experiences of introducing a new vendor into their networks," he says.

The latest funding will be used to develop further the icPhotonics chip

Somekh also says that using the router delivers revenue benefits. Replacing a traditional three-chassis - 126U in total - core router with the 6U one has enabled the operator to deploy servers in the resulting reclaimed space. Deploying the router with servers in colocation data centres has turned them from cost centres into revenue-generating ones.

The company said the latest raised funding will be used to develop further the icPhotonics chip. Compass-EOS has talked about a future chip with channels operating at 32Gbps. “We're also investing in innovative software and on the marketing side, focussing on the US market and Japan with a stronger presence there,” says Somekh.

The company also announced it has cut staff. There are now 100 people working at the company compared to 150 employed in March. "Looking at the strategy moving forward we decided to make these adjustments to better fit the objectives and financial plan," says Somekh.

The latest round of investment takes the total amount of funding raised by the start-up to over $162 million. Investors in the latest round include Comcast Ventures and Cisco Systems.

A Terabit network processor by 2015?

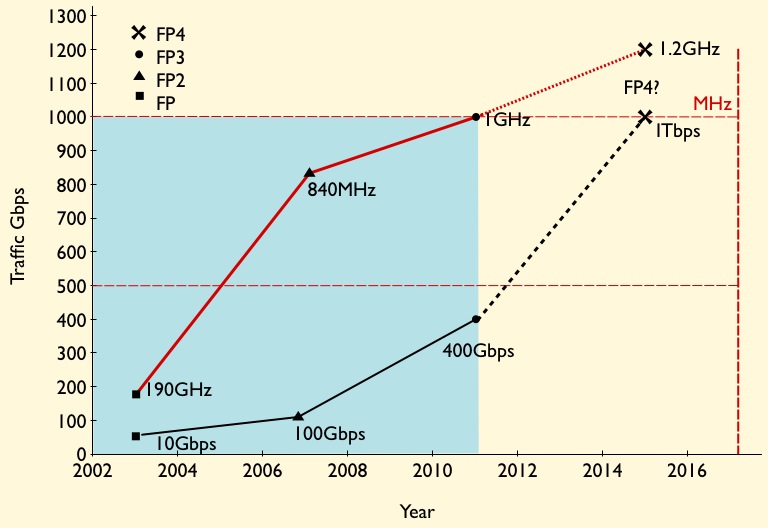

Given that 100 Gigabit merchant silicon network processors will appear this year only, it sounds premature to discuss Terabit devices. But Alcatel-Lucent's latest core router family uses the 400 Gigabit FP3 packet-processing chipset, and one Terabit is the next obvious development.

Source: Gazettabyte

Source: Gazettabyte

Core routers achieved Terabit scale awhile back. Alcatel-Lucent's recently announced IP core router family includes the high-end 32 Terabit 7950 XRS-40, expected in the first half of 2013. The platform has 40 slots and will support up to 160, 100 Gigabit Ethernet interfaces.

Its FP3 400 Gigabit network processor chipset, announced in 2011, is already used in Alcatel-Lucent's edge routers but the 7950 is its first router platform family to exploit fully the chipset's capability.

The 7950 family comes with a selection of 10, 40 and 100 Gigabit Ethernet interfaces. Alcatel-Lucent has designed the router hardware such that the card-level control functions are separate from the Ethernet interfaces and FP3 chipset that both sit on the line card. The re-design is to preserve the service provider's investment. Carrier modules can be upgraded independently of the media line cards, the bulk of the line card investment.

The 7950 XRS-20 platform, in trials now, has 20 slots which take the interface modules - dubbed XMAs (media adapters) - that house the various Ethernet interface options and the FP3 chipset. What Alcatel-Lucent calls the card-level control complex is the carrier module (XCM), of which there are up to are 10 in the system. The XCM, which includes control processing, interfaces to the router's system fabric and holds up to two XMAs.

There are two XCM types used with the 7950 family router members. The 800 Gigabit-per-second (Gbps) XCM supports a pair of 400Gbps XMAs or 200Gbps XMAs, while the 400Gbps XCM supports a single 400Gbps XMA or a pair of 200Gbps XMAs.

The slots that host the XCMs can scale to 2 Terabits, suggesting that the platforms are already designed with the next packet processor architecture in mind.

FP3 chipset

The FP3 chipset, like the previous generation 100Gbps FP2, comprises three devices: the P-chip network processor, a Q-chip traffic manager and the T-chip that interfaces to the router fabric.

The P-chip inspects packets and performs the look ups that determine where the packets should be forwarded. The P-chip determines a packet's class and the quality of service it requires and tells the Q-chip traffic manager in which queue the packet is to be placed. The Q-chip handles the packet flows and makes decisions as to how packets should be dealt with, especially when congestion occurs.

The basic metrics of the 100Gbps FP2 P-chip is that it is clocked at 840GHz and has 112 micro-coded programmable cores, arranged as 16 rows by 7 columns. To scale to 400Gbps, the FP3 P-chip is clocked at 1GHz (x1.2) and has 288 cores arranged as a 32x9 matrix (x2.6). The cores in the FP3 have also been re-architected such that two instructions can be executed per clock cycle. However this achieves a 30-35% performance enhancement rather than 2x since there are data dependencies and it is not always possible to execute instructions in parallel. Collectively the FP3 enhancements provide the needed 4x improvement to achieve 400Gbps packet processing performance.

The FP3's traffic manager Q-chip retains the FP2's four RISC cores but the instruction set has been enhanced and the cores are now clocked at 900GHz.

Terabit packet processing

Alcatel-Lucent has kept the same line card configuration of using two P-chips with each Q-chip. The second P-chip is viewed as an inexpensive way to add spare processing in case operators need to support more complex service mixes in future. However, it is rare that in the example of the FP2-based line card, the capability of the second P-chip has been used, says Alcatel-Lucent.

Having the second P-chip certainly boosts the overall packet processing on the line card but at some point Alcatel-Lucent will develop the FP4 and the next obvious speed hike is 1 Terabit.

Moving to a 28nm or an even more advanced CMOS process will enable the clock speed of the P-chip to be increased but probably not by much. A 1.2GHz clock would still require a further more-than-doubling of the cores, assuming Alcatel-Lucent doesn't also boost processing performance elswhere to achieve the overall 2.5x speed-up to a 1 Terabit FP4.

However, there are two obvious hurdles to be overcome to achieve a Terabit network processor: electrical interface speeds and memory.

Alcatel-Lucent settled on 10Gbps SERDES to carry traffic between the chips and for the interfaces on the T-chip, believing the technology the most viable and sufficiently mature when the design was undertaken. A Terabit FP4 will likely adopt 25Gbps interfaces to provide the required 2.5x I/O boost.

Another even more significant challenge is the memory speed improvement needed for the look up tables and for packet buffering. Alcatel-Lucent worked with the leading memory vendors when designing the FP3 and will do the same for its next-generation design.

Alcatel-Lucent, not surprisingly, will not comment on devices it has yet to announce. But the company did say that none of the identified design challenges for the next chipset are insurmountable.

Further reading:

Network processors to support multiple 100 Gigabit flows

A more detailed look at the FP3 in New Electronics, click here