Credo has unveiled its Blue Heron retimer chip, designed for line cards used in AI servers.

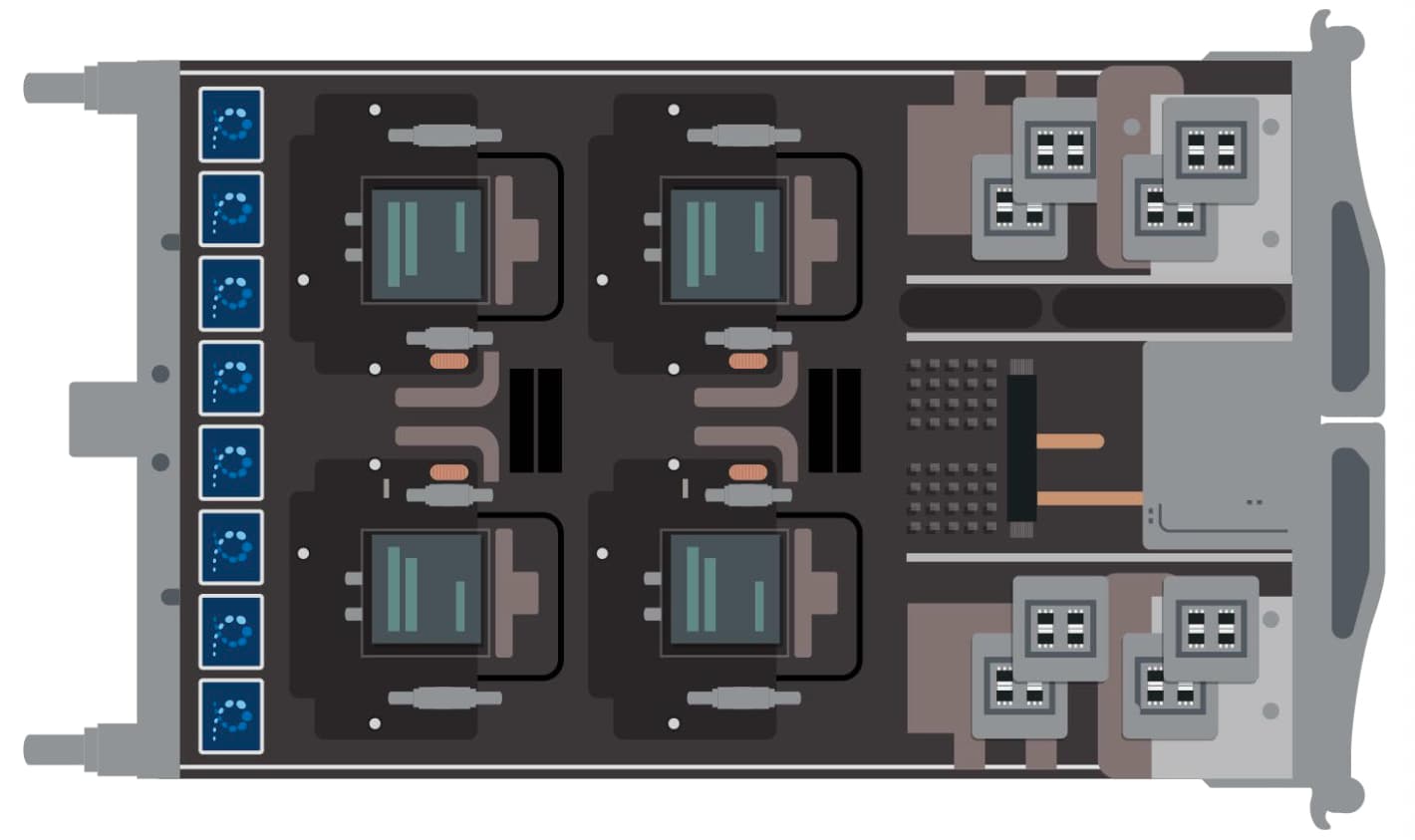

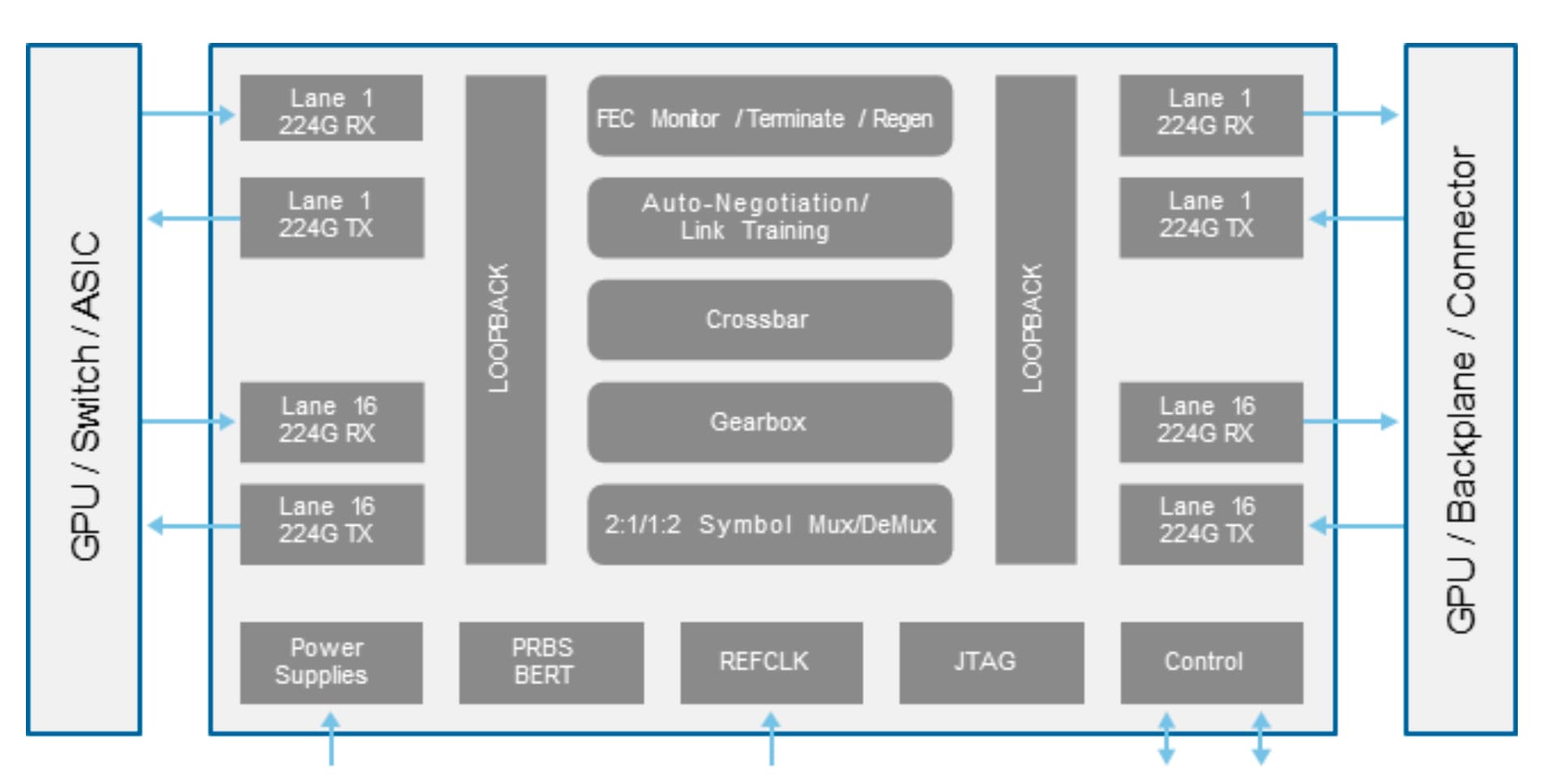

Blue Heron uses 224-gigabit serialiser-deserialisers (SerDes) for a total capacity of 3.2 terabits: 16 lanes in and 16 lanes out.

Credo has long supplied line-card retimer chips, at 56-gigabit, 112-gigabit, and now at 224-gigabit line rates. Such retimers are already used for scale-out networking.

What excites Credo is AI scale-up: the opportunity to keep growing the number of AI accelerator chips such that processing performance scales linearly.

This requires high-bandwidth links and the ability to use copper across long links.

“We’re positioning the Blue Heron line card device for scale-up networking,” says Sandeep Shah, Assistant Vice President for Credo’s Retimer Products. “As scale-up moves from proprietary to using an Ethernet PHY (physical layer device), it’s a huge opportunity for us.”

To this end, Blue Heron’s physical layer supports key emerging scale-up protocols, such as UALink, ESUN, and Ethernet.

Supporting multiple protocols ensures the retime aligns with broader data centre ecosystems while avoiding overcommitment to proprietary interconnect schemes.

Revenue growth

Credo has achieved significant revenue growth in the last two years.

Revenues were up 226% year-on-year to $437 million in fiscal year 2025 (ending April ‘25), while for fiscal year 2026, revenues are expected to more than double again (up 251%) to $1.19 billion.

The company’s growth can be directly attributed to the networking needs of AI racks used by the hyperscalers, in large part due to its active electrical cable portfolio. Its retimer ICs have long been used in data centre switches and router platforms. Now Credo is eyeing the AI scale-up opportunity.

From 112G to 224G: A Nonlinear Challenge

Doubling the speed from 112 gigabit-per-second (Gbps) to 224Gbps with a SerDes IC while maintaining existing reaches is a considerable engineering undertaking.

On paper, electrical reach roughly halves when lane speed doubles. In practice, careful retimer design can claw back some distance.

Power per bit also rises from 112 gigabit to 224 gigabit, though engineering efforts aim to optimise efficiency at the bit level.

The trade-off is clear: higher performance and extended reach come at the cost of increased complexity and silicon investment.

Why 3nm CMOS

Credo has long marketed an “N minus one” philosophy—delivering competitive power and signal performance using an older CMOS process node than competitors. If similar performance can be achieved using a more mature CMOS node, cost and supply advantages follow.

Credo says the pattern no longer applies at 224 gigabit. Credo’s Blue Heron uses a 3nm CMOS process due to the complexity of the digital signal processing.

For 224-gigabit 4-level pulse-amplitude modulation (PAM4) signalling, the transmitter and receiver requirements scale nonlinearly. Channel loss budgets around 40dB become significantly harder to close, given that receiver equalisation demands are higher.

Earlier 112-gigabit designs used 21 receiver filter taps. Credo has increased the number of taps substantially to 30 for fast-forward equalisation, compensating for signal distortion introduced by the channel at 224 gigabit. An extra 16 taps are also used to manage reflections, noise, and inter-symbol interference. Equalisation must be more precise and adaptive at 224 gigabit, which makes it more computationally intensive.

Link training to establish a stable link takes about 10 seconds, during which the device characterises the channel and configures the equaliser. But after the link-up stage, adaptation continues. Temperature changes, for example, can subtly alter channel characteristics, and the retimer compensates to prevent rising bit-error rates and the risk of burst errors.

Firmware running on an embedded microcontroller inside the device orchestrates these calibration and adaptation routines.

The 224-gigabit Blue Heron line card retimer’s 16 lanes in and 16 lanes out is common across retimer generations. With 16, 224-gigabit SerDes, a Blue Heron chip supports flexible configurations: two 1.6-terabit ports, four 800-gigabit ports, or other combinations.

Looking towards 448 gigabit links

The next step—448-gigabit SerDes—will test copper’s limits, standardisation work that the OIF has already started.

Whether copper can stretch meaningfully beyond inside-rack distances at 448 gigabit remains an open question.

For now, 224 gigabit represents a balancing act. Reach drops modestly, digital signal processing complexity rises sharply, and silicon has to move to a leading-edge node. But AI system densification may give copper more room than previously assumed.

Inside compact GPU clusters, the economics of copper—augmented by increasingly sophisticated retimers—works, claims Credo.

Copper’s advancement may require ever more engineering effort and advanced CMOS but it is not retreating quietly.