-

-

-

-

-

PAM-4 may not carry 448G electrical signalling all the way

-

The OIF is leaning toward a reach-dependent roadmap, not one universal solution

-

Optimisation may have to broaden from the SerDes to the rack.

-

-

-

-

The industry keeps progressing in its ability to push more bits down a wire. It has always been challenging to double the transmitted bit rate, but there was headroom to speed up the serialiser/deserialiser (SerDes) circuitry every few years.

But now the OIF, the industry organisation tasked with doubling copper electrical interface speeds to 448 gigabit-per-second (Gbps), must consider more complex techniques and do its work more quickly due to AI’s scaling needs.

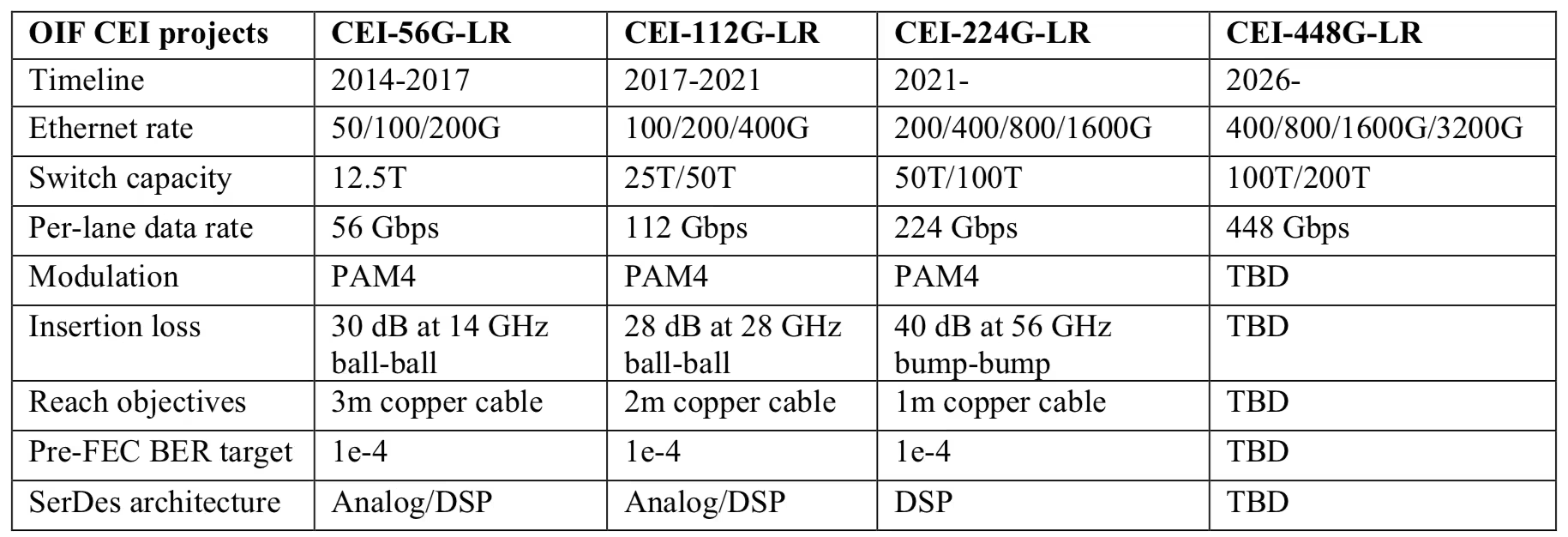

Around a decade ago, the OIF moved from simple non-return-to-zero (NRZ) signalling to 4-level pulse-amplitude-modulation (PAM-4) to double speeds to 56Gbps, known as CEI-56G (Common Electrical I/O). PAM-4 enabled a doubling of the bit rate while using existing 26-28 gigabaud (GBd) components.

PAM-4 was also used for the next two OIF CEI standards, at 112Gbps and 224Gbps. But for the latest 448Gbps standard under development, it is already evident that PAM-4 may not be enough.

When the CEI-448G work began in August 2024, the OIF involved other industry-standard bodies for the first time.

“We collectively understood that 448 gigabit is going to be more challenging for various reasons, including the laws of physics,” says Nathan Tracy, OIF president and technologist, system architecture team at TE Connectivity.

The OIF started pulling together a CEI-448G framework document and circulated it to gain input from various sources. The aim was to galvanise and create a unified position before publishing the document for wider circulation in November.

Delivering reach

The new standard must not only double the data rate from 224Gbps to 448Gbps but also try to retain the reach of previous CEI standards. “That is an exceptional challenge,” says Cathy Liu, the OIF vice president, distinguished engineer and director at Broadcom.

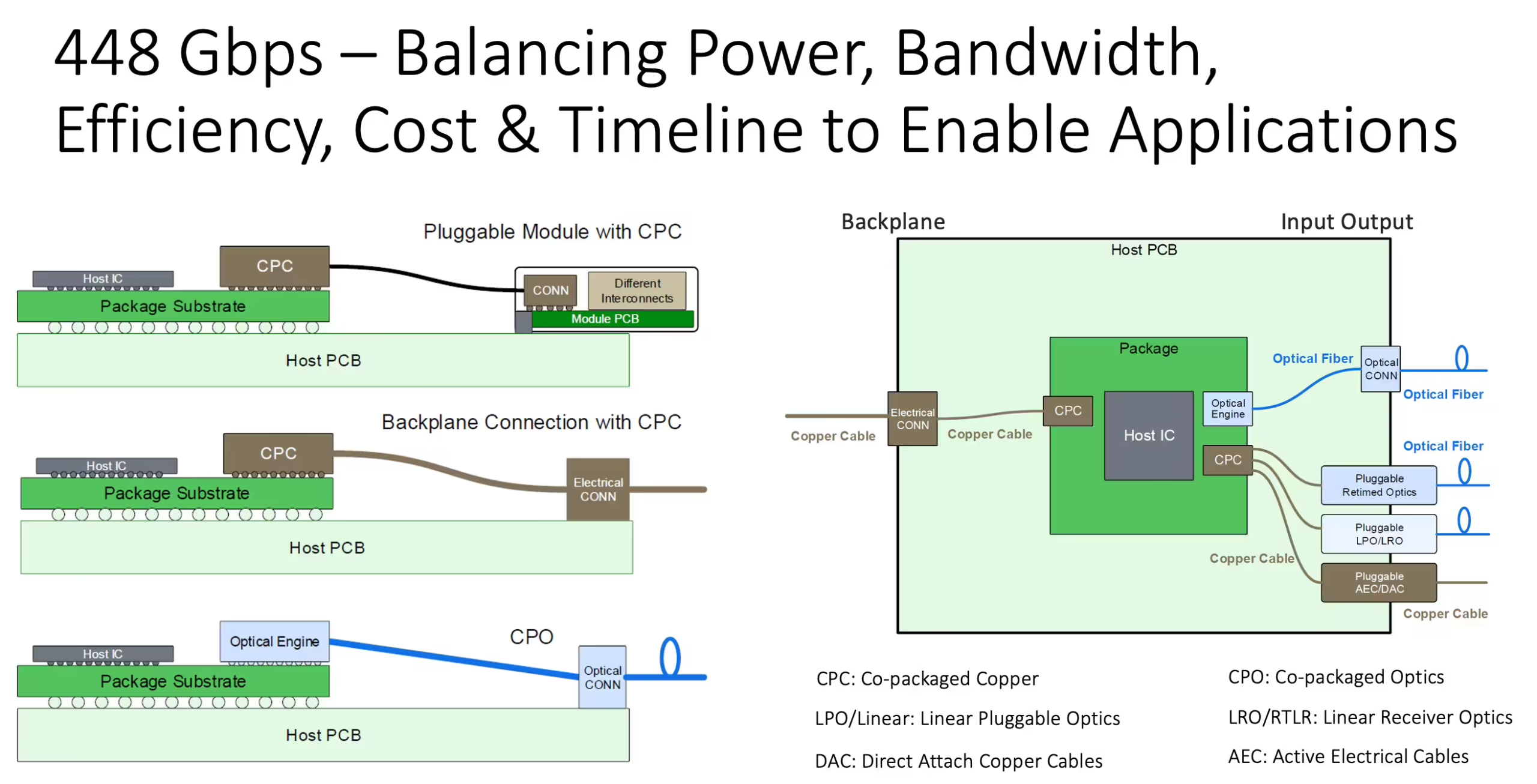

The OIF CEI work involves developing specifications, published as OIF Implementation Agreement documents, for different reaches. The shortest reaches are between dies, between a die and an optical engine within a package, and between separate dies near to each other. These applications fall under CEI-XSR and CEI-XSR+ (extremely short reach interfaces).

Connecting the host chip to a pluggable module requires the OIF’s very short-reach (CEI-VSR) interface. The next reach range is medium reach (MR), typically to connect chips on a printed circuit board.

The most challenging is the Long Reach (LR) spec, which can pass through a backplane to connect chassis in a rack or between adjacent racks. The challenge the OIF faces is that doubling the symbol rate while maintaining the same reach collides head-on with channel bandwidth limits and impairments.

Using PAM-4 at 448Gbps corresponds to a symbol rate of 224GBd, which in Nyquist terms implies a channel bandwidth of 112GHz. The OIF’s work group members have yet to achieve such a bandwidth, but progress is being made.

“Starting in October 2024, we were looking at channels that were rolling off at 75-80GHz; now we’re seeing channels approaching 100GHz,” says Tracy. Still short of 112GHz, but notable progress nonetheless. It also helps clarify the equalisation schemes that will be needed.

One solution is to adopt higher PAM schemes such as PAM-6 or PAM-8 to relax the analogue bandwidth. PAM-6 reduces the baud rate to around 174GBd and the analogue bandwidth from 112GHz to 90GHz, while PAM-8 reduces the baud rate further to 150GBd and a 75GHz bandwidth.

The higher-order PAMs may relax the analogue bandwidth targets but place greater demand on the receiver’s digital signal processor (DSP) tasked with recovering the greater number of bits per symbol.

OIF’s reasoning

The likelihood is that the work will start with the most challenging LR specification. “If we can do the long reach, then we can also support the chip-to-module, the VSR application and XSR, which is more targeted at the co-packaged optics application,” says Liu.

For LR, the aim is to span backplanes and chassis interconnect using copper cables. There will also be work on linear-drive and half-retimed designs, as these promise lower power consumption.

The OIF is cautiously optimistic about reach. “We’ve looked at channels at 400 gigabit that suggest that at least a meter of reach may be possible,” says Tracy. “It’s not a slam dunk; everything that we get will be hard fought for.”

Liu says that reach and low power are almost orthogonal requirements. The OIF challenge, she says, is to come up with solutions that meet these ‘orthogonal’ requirements.

For LR, it requires advances in connectors, equalisation schemes, and forward error correction (FEC) to counter channel impairments.

“Even with the improvement we have seen, there’s still a challenge existing in the channel loss and the crosstalk reflections, which is limited to a bandwidth of 90GHz,” says Liu.

That makes using 448G PAM-4 extremely challenging.

Connecting the host chip to the pluggable module, the OIF is optimistic that over time 120GHz will be possible, but the issue is that solutions are needed sooner. “It’s a very dynamic world we are in,” says Tracy.

Liu outlines that the OIF’s thinking is a staged, reach-dependent strategy that allows the industry to ship something soon to meet AI’s demanding networking needs even as channel limitations persist.

Liu outlines a world where different reaches adopt different solutions: PAM-4 may be possible for shorter reaches, while higher modulation schemes – PAM-6 or PAM-8 – may be required for longer reaches, considering the 90GHz channel reality.

The OIF stresses this is not yet policy. “We maybe diverge based on the different application spaces, the debating is still happening,” says Liu. But hard calls are approaching.

Crucially, Liu points out that the issue of backward compatibility will change if the industry adopts higher-order PAM schemes soon. Indeed, she argues it is an advantage if the OIF starts with higher-order PAM now because if channels improve later, the transition to future speeds (CEI-896G?) will be smoother.

“Don’t assume the ‘lowest PAM wins’ permanently—sometimes the industry keeps a higher-order scheme because it becomes a stepping-stone to the next throughput jump,” says Liu.

If a higher-order PAM is adopted, the need for more DSP assistance will be helped by continual advances in CMOS process nodes.

“When you’re using the higher modulation schemes, you can reduce the baud rate, so the analogue is easier, but then more complicated detection is needed,” says Liu. Yet more gates are a byproduct of more advanced CMOS nodes. So, putting the burden on the DSP rather than the analogue bandwidth may be the better approach.

About FEC schemes, Liu acknowledges the classic trade-off: higher modulation schemes require more advanced FEC, but the key is not to overdo it, as the price is greater power consumption.

The rack as a unit of optimisation

Tracy notes that the decisions regarding 448G can’t be evaluated just from a SerDes perspective since the optimisation target is shifting upwards.

“We need to think about the rack as the smallest building block that matters instead of thinking about host silicon,” says Tracy.

At this higher system scale, trade-offs may invert: “If we increase power dissipation a little bit at the silicon level, but at the rack level, it gives us a lower aggregate power, then that’s an important consideration,” he says.

That’s the subtext behind the entire 448G framework: the industry is choosing not just an electrical interface, but an evolution path for in-rack architecture under three key constraints, says Tracy. The first is a physical one – the bandwidth, reach, and noise, the second is economic: cost and power consumed, and the third is operational: deploying not just at scale but hyperscaler scale.

The pressure to move fast is already here: “Truly, the time is upon us,” says Tracy.